# INVESTIGATION OF THE CHANNEL HOT CARRIER (CHC) STRESSING EFFECTS AND IDENTIFICATION OF THE STRESSINDUCED OXIDE TRAPS LEADING TO RTS IN PMOSFETS

by

### TANVIR AHMED

# Ph.D. Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Arlington in Partial Fulfillment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

The University of Texas at Arlington

December 2020.

Copyright © by Tanvir Ahmed 2020

#### Acknowledgements

First of all, I would like to convey my sincerest gratitude towards my professor Dr. Zeynep Celik-Butler, for providing me the opportunity to conduct research in the field of device noise and reliability. Throughout these years of my Ph.D. journey, her constant supervision and guidance have played a crucial role in designing the experiments and carrying out the researches. The weekly research meetings with her have been motivational and inspirational to bring out new ideas. In addition, whenever I had a hard time with any of the research issues, she was always helpful to find a solution.

I like to thank my Ph.D. proposal and dissertation committee members - Dr. Jonathan Bredow, Dr. Michael Vasilyev, Dr. Weidong Zhou, and Dr. Yan Wan. I appreciate their time to review the dissertation and provide their valuable insights and comments. I also thank the academic advisors and staff of the EE department.

I appreciate the support provided by my former colleagues in the lab - Dr. A S M Shamsur Rouf, Dr. Sk Rubaiyat Tousif, Dr. Md. Sohel Mahmood, Dr. Sajeeb Raihan, and Dr. H M Ashfiqul Hamid. I also greatly value the friendship they have shown towards me.

Finally, I would like to express my heartfelt thanks to my family. They have provided me inspiration throughout these years. Their constant prayers have motivated me to attain my goals and complete this long journey.

October 2020.

#### Abstract

Investigation of the Channel Hot Carrier (CHC) Stressing Effects and Identification of the Stress-Induced Oxide Traps Leading to RTS in pMOSFETs

#### Tanvir Ahmed

The University of Texas at Arlington, 2020

Supervising Professor: Dr. Zeynep Celik-Butler

Electrical stressing mechanisms are responsible for the generation of stress-induced gate SiO<sub>2</sub> defects, in addition to the presence of process-induced oxide traps, in MOSFETs. Random telegraph signal (RTS) can be utilized as a tool to characterize these defects. Channel hot carrier (CHC) stressing is reported to result in the worst degradation in pMOSFETs. However, the effects of CHC on RTS for pMOSFETs are underreported. The main objective of this work is to investigate the impact of the CHC stressing on pMOSFETs by analyzing RTS. For this reason, the effects of CHC stressing on different RTS parameters are examined. Additionally, responsible defect sites are identified.

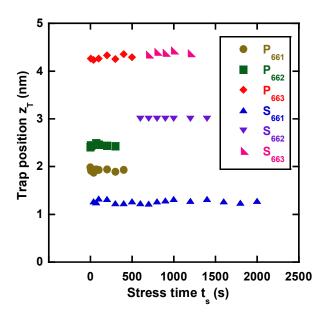

At first, CHC stressing is conducted for up to 2000 seconds with variable time intervals of 5 seconds to 200 seconds under room temperature. Then, different RTS parameters are inspected to study the impact of CHC stressing. The investigated RTS parameters are average carrier capture and emission times by the trap, trap position, trap energy level with respect to the oxide valence band edge, capture cross-section, RTS amplitude, and screened scattering coefficients. CHC stressing does not impact the position of the trap and the trap energy level with respect to the oxide valence band edge. The decrease of relaxation energy is considered to be responsible for the change in average capture time and capture cross-section with stressing for the stress-induced traps. However, further investigations are required which would focus on variable temperature measurements. The generated fixed positive oxide charges result in additional charge screening on the traps with stressing. Therefore, the Coulomb screened scattering coefficient decreases. As a result, the amount of mobility fluctuations is lowered, and we observe an increase in RTS amplitude with stressing. The novelty of this work lies in the fact that the two-dimensional mobility fluctuations model is implemented for the very first time to theoretically determine the screened scattering coefficients under CHC stressing in pMOSFETs. Later, these theoretically determined screened scattering coefficients are compared with the measured ones.

Moreover, detailed studies of the thermal activation process and structural relaxation energies are required to identify the defect centers under CHC stressing. Therefore, performing the variable temperature RTS

measurements is necessary. To fully characterize the defects, variable temperature RTS measurements are conducted from room temperature down to 215 K. CHC stressing is performed for up to 1200 seconds. Additional RTS trap parameters such as capture activation energy, emission activation energy, relaxation energy, change in enthalpy, and change in entropy are determined. Faster capture times are exhibited by the stress-induced traps, which result from the larger trap capture cross-sections. A pronounced difference is observed in the change of entropy among the process- and stress-induced traps upon hole emission from the defect site to the Si valence band. This points to the possibility of a different structural defect being responsible behind the stress-induced traps than the native ones. Two different types of defects, D-III Si and hydrogen bridge are identified as the trapping center in SiO<sub>2</sub> for the pMOSFETs under CHC stressing.

Like RTS, flicker (1/f) noise has also been a prominent source of noise in MOSFETs. Our goal is to find ways to passivate the traps and thereby minimize the amount of 1/f noise. 1/f noise PSD measurements are carried on nMOSFETs from three different wafers. Then the current noise PSD data are normalized with respect to the channel width, length, and oxide layer thickness. Later, 1/f noise PSD data are curve fitted to the unified numbers and mobility fluctuations (UNMF) model to determine the trap density and the screened scattering coefficients. The normalized 1/f noise data are correlated with the fabrication steps across the wafers. By incorporating necessary changes in the fabrication steps, 1/f noise can be minimized.

# **Table of Contents**

| Acknowledgements                                                                 | iii          |

|----------------------------------------------------------------------------------|--------------|

| Abstract                                                                         | iv           |

| Table of Contents                                                                | vi           |

| List of Figures                                                                  | viii         |

| List of Tables                                                                   | xii          |

| List of Symbols                                                                  | xiii         |

| Chapter 1: Introduction                                                          | 1            |

| 1.1 Background and Motivations Behind the Research Work                          | 1            |

| 1.2 Different Types of Electrical Noise                                          | 5            |

| 1.2.1 Thermal Noise                                                              | 5            |

| 1.2.2 Generation-Recombination Noise                                             | 6            |

| 1.2.3 Random Telegraph Signal (RTS) Noise                                        | 6            |

| 1.2.4 Flicker Noise                                                              | 9            |

| 1.2.4.1 Number Fluctuations Model                                                | 10           |

| 1.2.4.2 Mobility Fluctuations Model                                              | 14           |

| 1.2.4.3 Correlated Mobility Fluctuations Model                                   | 15           |

| 1.2.4.4 Unified Number and Mobility Fluctuations Model                           | 16           |

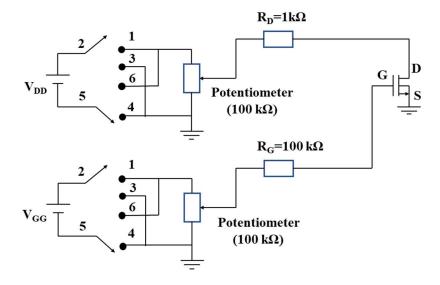

| Chapter 2: Noise Measurement Procedures and Setup                                | 20           |

| 2.1 DC Measurements                                                              | 20           |

| 2.2 C-V Measurements                                                             | 21           |

| 2.3 Setup for Flicker (1/f) Noise Measurements and Procedures                    | 24           |

| 2.4 RTS Noise Measurements Under Channel Hot Carrier (CHC) Stressing             | 26           |

| 2.5 Experimental Setup for RTS Measurements Under Variable Temperatures          | 27           |

| Chapter 3: RTS Trap Parameters in pMOSFET                                        | 29           |

| 3.1 Average Capture and Emission Times                                           | 29           |

| 3.2 Energy Level and Position of The Trap                                        | 31           |

| 3.3 RTS Amplitude and Screened Scattering Coefficient                            | 33           |

| 3.4 Trap Capture Cross-section                                                   | 35           |

| 3.5 Capture Activation Energy and Capture Cross-section Pre-factor               | 38           |

| 3.6 Emission Activation Energy                                                   | 39           |

| 3.7 Relaxation Energy                                                            | 40           |

| Chapter 4: Channel Hot Carrier (CHC) Stressing Effect on Room Temperature RTS Pa | arameters 43 |

| 4.1 RTS Measurements and Device Specifications                                   | 43           |

| 4.2 Trap Position and Energy Level                                                                           | 44   |

|--------------------------------------------------------------------------------------------------------------|------|

| 4.3 Effect of Stressing on Trap Stability                                                                    | 47   |

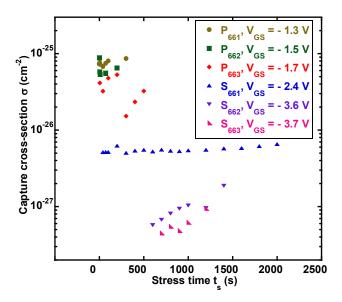

| 4.4 Effect of Stressing on Trap Capture Cross-section                                                        | 48   |

| 4.5 Effect of Stressing on Screened Scattering Coefficients                                                  | 51   |

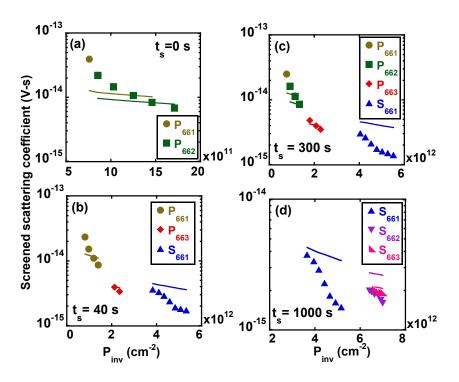

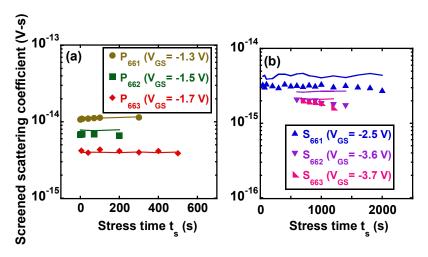

| 4.5.1 Modeling Quantization Effects on Screened Scattering Coefficients                                      | 52   |

| 4.5.2 Two-dimensional Mobility Fluctuations Model for pMOSFET                                                | 56   |

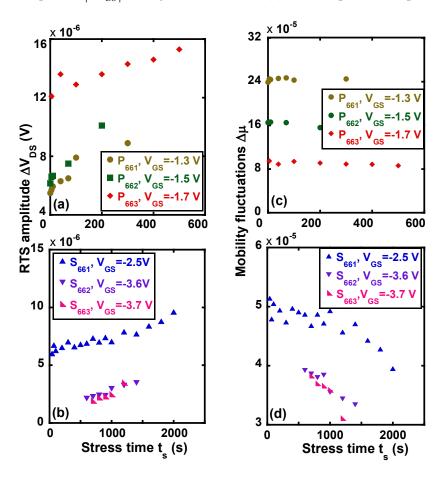

| 4.6 Effect of Stressing on RTS Amplitude                                                                     | 58   |

| Chapter 5: Identification of Channel Hot-Carrier Stress-Induced Oxide Traps in pMOSFET                       | s 60 |

| 5.1 RTS Measurement Technique                                                                                | 60   |

| 5.2 RTS Analyses Procedures and Results                                                                      | 62   |

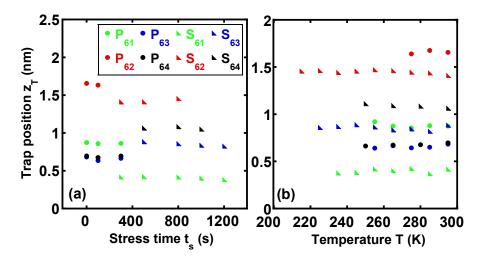

| 5.2.1 Trap Position and Energy Level                                                                         | 64   |

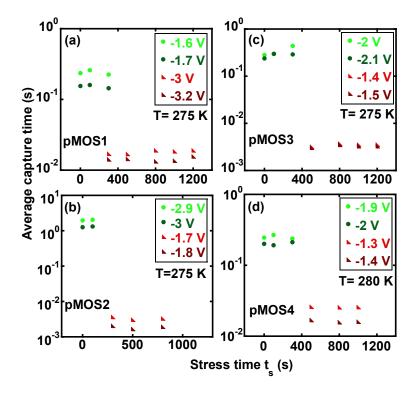

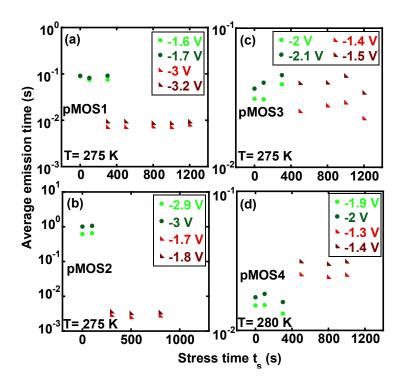

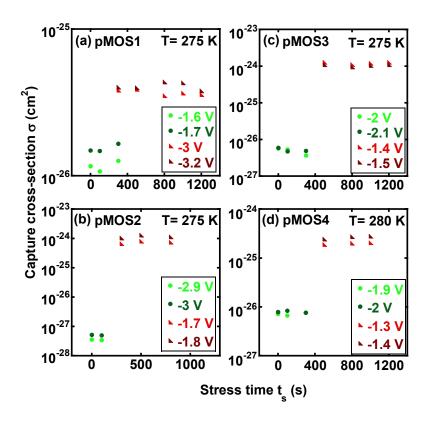

| 5.2.2 Trap Time Constants and Capture Cross-Section                                                          | 66   |

| 5.2.3 Effect of Stressing on RTS Amplitudes                                                                  | 68   |

| 5.2.4 Activation Energies of Traps from RTS Data                                                             | 70   |

| 5.3 Identification of the Defect Centers                                                                     | 73   |

| Chapter 6: Analyses of Flicker Noise in nMOSFETs                                                             | 77   |

| 6.1 Specification of the nMOSFET Devices and Measurement Steps                                               | 78   |

| 6.2 Mathematical Analysis of the 1/f Noise Data                                                              | 80   |

| 6.3 Normalization of the Flicker (1/f) Noise Data                                                            | 82   |

| 6.4 Correlation of the Process Parameters with 1/f Noise across Different Wafers                             | 87   |

| 6.5 Extraction of Trap Density and Screened Scattering Coefficient Parameters Based on t Unified Noise Model |      |

| 6.6 Comparison between the Normalized Number and Mobility Fluctuations for the Large Dimension Devices       | 91   |

| Chapter 7: Conclusions                                                                                       | 93   |

| References                                                                                                   | 96   |

# **List of Figures**

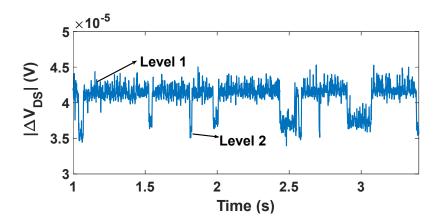

| Fig. 1. 1 Two level RTS signal. The transition between level 1 and 2 indicates the presence of a single                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| trap                                                                                                                                                                 |

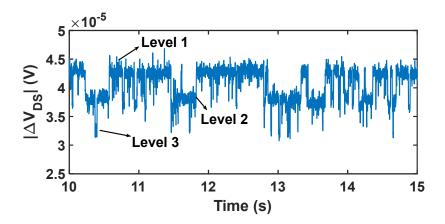

| Fig. 1. 2 Three level RTS signal. The transition from level 1 to 2 indicates the presence of one trap. The                                                           |

| transition from level 2 to 3 indicates the presence of another trap at the same time span of the recorded                                                            |

| data                                                                                                                                                                 |

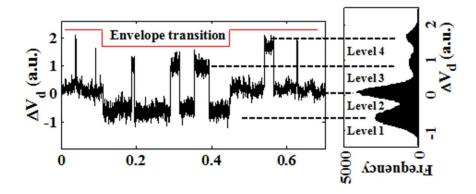

| Fig. 1. 3 The presence of envelope transition in a multi-level RTS signal [62]                                                                                       |

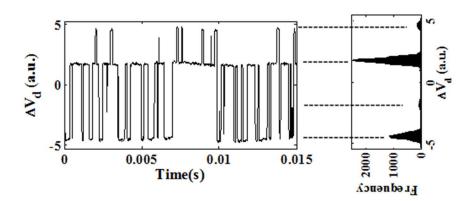

| Fig. 1. 4 The presence of envelope transition in a multi-level RTS signal [62]                                                                                       |

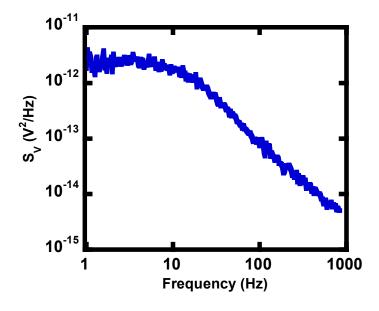

| Fig. 1. 6 The voltage noise PSD of a flicker (1/f) noise. The slope in this case is very close to 1, which is                                                        |

| agreeing to be within the range of 0.7-1.4.                                                                                                                          |

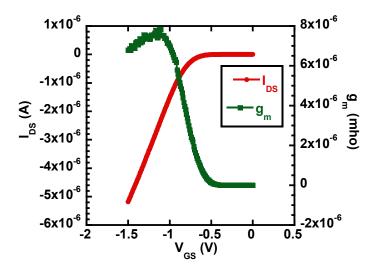

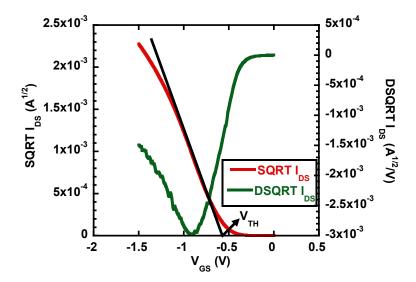

| Fig. 2. 1 Drain source current $I_{DS}$ and channel transconductance $g_m$ as a function of gate-source voltage                                                      |

| $V_{GS}$ for a pMOSFET.                                                                                                                                              |

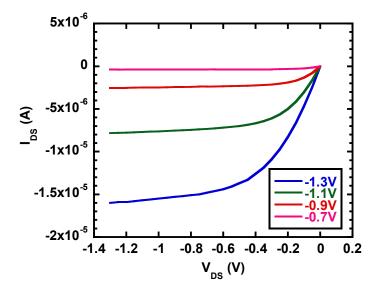

| Fig. 2. 2 Drain source current $I_{DS}$ as a function of drain-source voltage $V_{DS}$ for different $V_{GS}$ values of a                                            |

|                                                                                                                                                                      |

| pMOSFET                                                                                                                                                              |

|                                                                                                                                                                      |

| denotes $V_{TH}$                                                                                                                                                     |

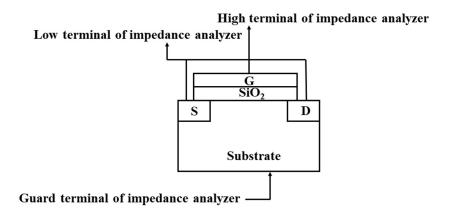

| Fig. 2. 4 C-V measurement setup                                                                                                                                      |

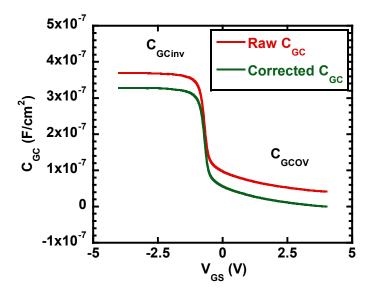

| Fig. 2. 5 C-V characteristic plot of a MOS capacitor                                                                                                                 |

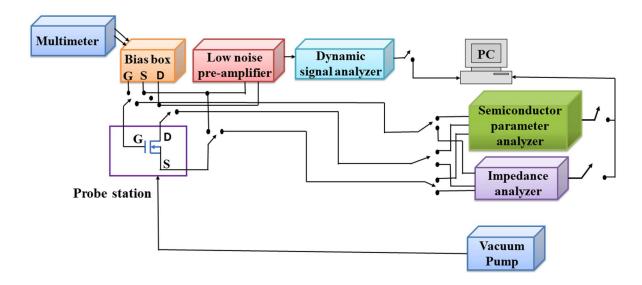

| Fig. 2. 6 Flicker (1/f) noise measurement setup                                                                                                                      |

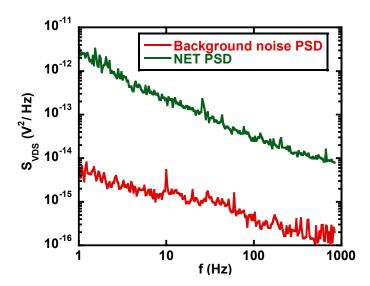

| Fig. 2. 8 Background noise and net power spectral density (PSD) of a nMOSFET                                                                                         |

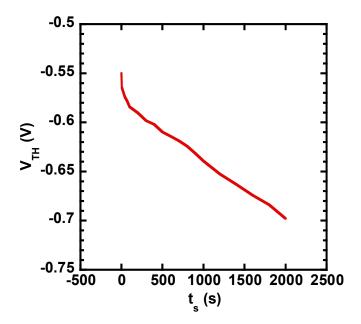

| Fig. 2. 9 Degradation of threshold voltage $V_{TH}$ as a function of stressing time $t_s$ for a pMOSFET26                                                            |

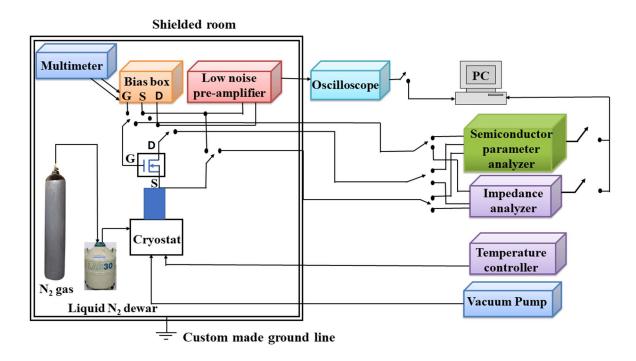

| Fig. 2. 10 RTS noise measurement setup under variable temperature. $\frac{1}{2}$                                                                                     |

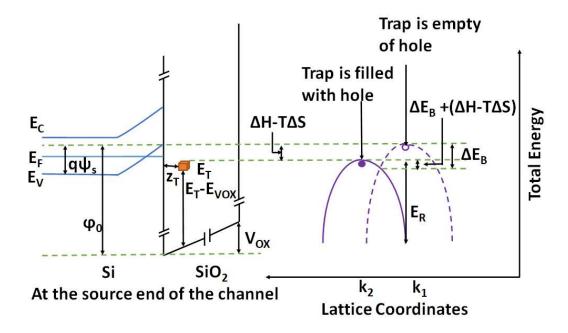

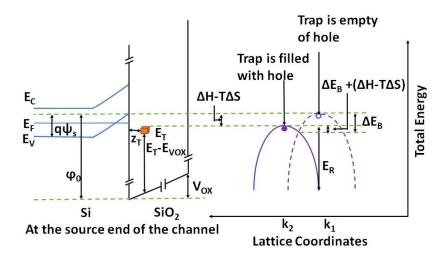

| Fig. 3. 1 Energy band diagram of a pMOSFET at the source end of the channel                                                                                          |

| Fig. 3. 2 Configuration co-ordinate diagram of a pMOSFET                                                                                                             |

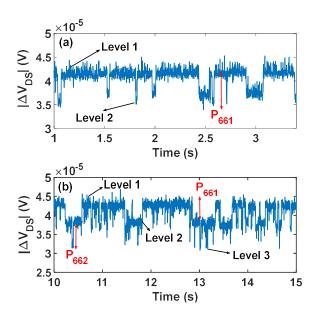

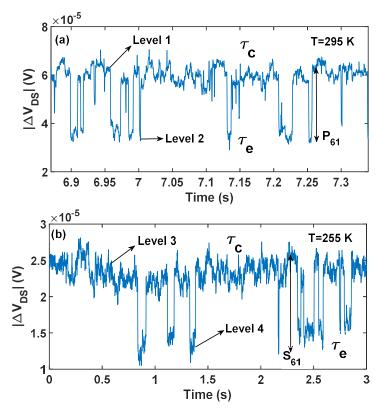

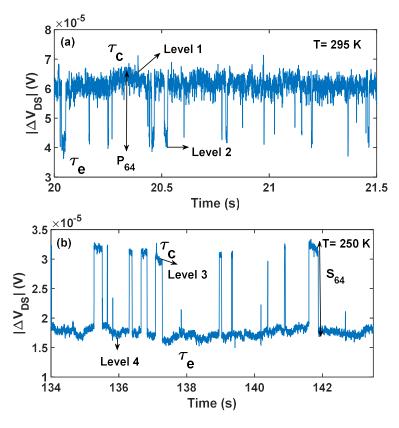

| Fig. 4. 1 (a) Two level RTS signal observed on the fresh device at $V_{GS} = -1.0$ V due to the first process-                                                       |

| induced trap $P_{661}$ . (b) Three level RTS signal observed in the fresh device at $V_{68} = -1.1$ V. Transition from                                               |

| level 1 to 2 denotes presence of the process-induced trap $P_{661}$ and transition from level 2 to 3 denotes                                                         |

| presence of the second process-induced trap $P_{662}$                                                                                                                |

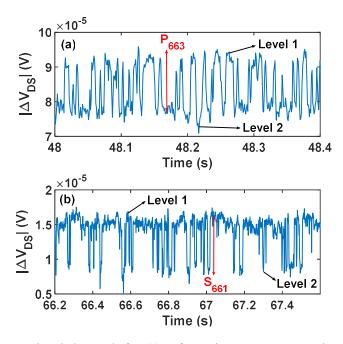

| Fig. 4. 2 (a) Two level RTS signal observed after 40 s of stressing at $V_{GS} = -1.7$ V due to the process-                                                         |

| induced trap $P_{663}$ . (b) Two level RTS signal observed after 70 s of stressing at $V_{68} = -2.6$ V denotes trap                                                 |

| S <sub>661</sub>                                                                                                                                                     |

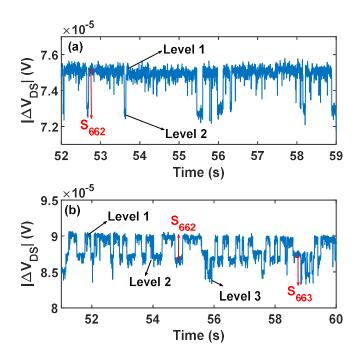

| Fig. 4. 3 (a) Two level RTS signal observed after 700 s of stressing at $V_{GS} = -3.5$ V due to the stress-                                                         |

| induced trap S <sub>662</sub> . (b) Three level RTS signal observed after 800 s of stressing at $V_{GS} = -3.65$ V. Transition                                       |

|                                                                                                                                                                      |

| from level 1 to 2 denotes presence of the stress-induced trap $S_{662}$ and transition from level 2 to 3 denotes presence of the other stress-induced trap $S_{663}$ |

| <u>*</u>                                                                                                                                                             |

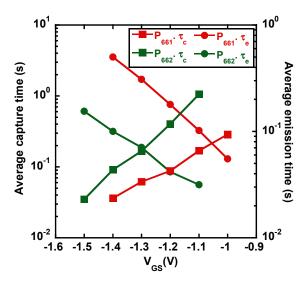

| Fig. 4. 4 Average capture time $\overline{\tau}_c$ and emission time $\overline{\tau}_e$ as a function of gate to source voltage for two of                          |

| the process-induced traps $P_{661}$ and $P_{662}$ present in the fresh device.                                                                                       |

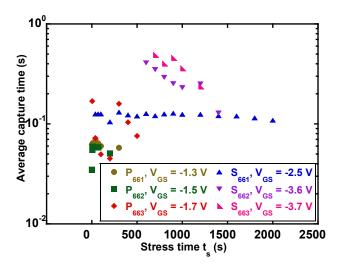

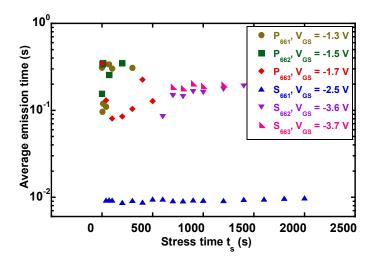

| Fig. 4. 5 Average capture time $\bar{\tau}_c$ as function of stress time $t_s$ for all the traps. $\bar{\tau}_c$ is observed to be                                   |

| decreasing with stressing for two of the stress-induced traps S <sub>662</sub> and S <sub>663</sub>                                                                  |

| Fig. 4. 6 Average emission time $\overline{\tau}_e$ as a function of stress time $t_s$ for all the traps. It is not changing                                         |

| significantly with stressing for the traps                                                                                                                           |

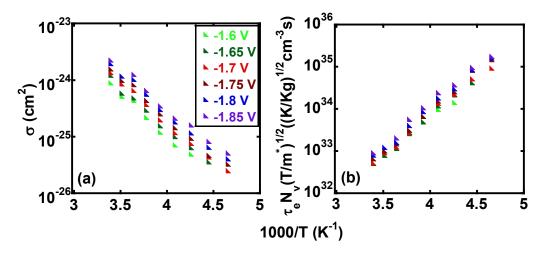

| Fig. 5. 9 Arrhenius plot of S <sub>63</sub> for different $V_{GS}$ values at $t_s = 300$ s for the (a) capture cross-section $\sigma$ ,                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| from which capture activation energy $\Delta E_B$ is computed. (b) The normalized mean emission time, from                                                                                                                                     |

| which change in enthalpy $\Delta H$ and change in entropy $\Delta S/k_B$ are determined                                                                                                                                                        |

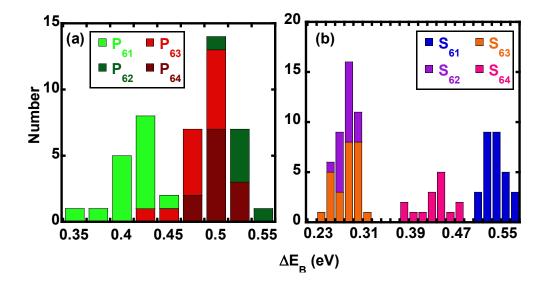

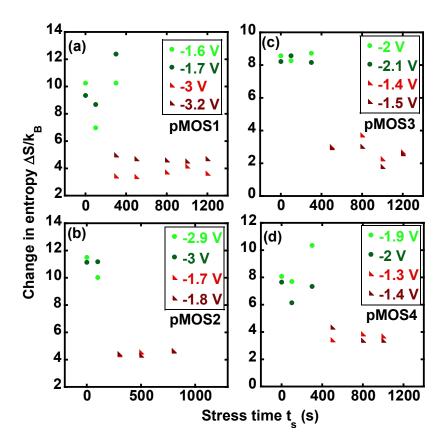

| Fig. 5. 10 Distribution of the capture activation energy $\Delta E_B$ for all the stressing time instances for the (a)                                                                                                                         |

| process-induced, (b) stress-induced traps of all the reported devices                                                                                                                                                                          |

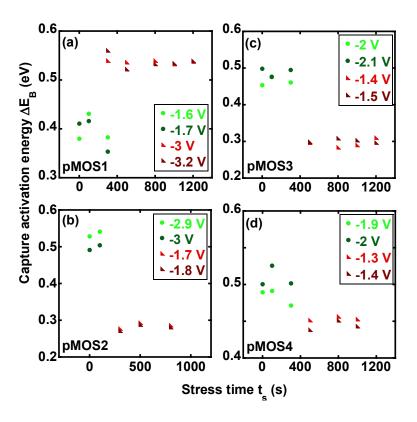

| Fig. 5. 11 Capture activation energy $\Delta E_B$ as a function of stressing time $t_s$ for representative $V_{GS}$ values.                                                                                                                    |

| 70                                                                                                                                                                                                                                             |

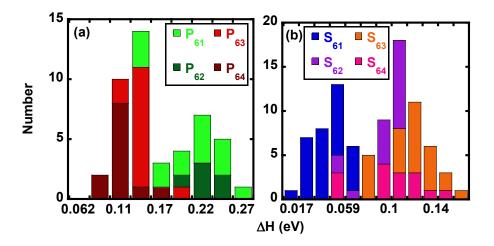

| Fig. 5. 12 Distribution of the change in enthalpy $\Delta H$ under stressing time instances for the (a) process-induced, (b) stress-induced traps                                                                                              |

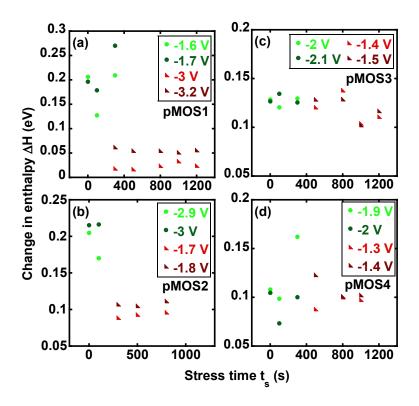

| Fig. 5. 13 Change in enthalpy $\Delta H$ as a function of stressing time $t_s$ for the representative $V_{GS}$ values 71                                                                                                                       |

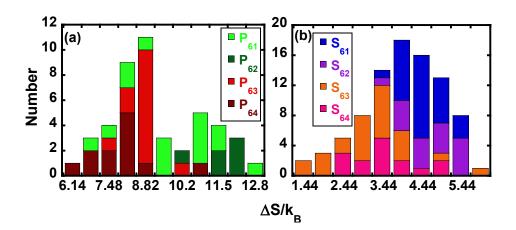

| Fig. 5. 14 Distribution of the change in entropy $\Delta S/k_B$ under all the stressing time instances for the (a)                                                                                                                             |

| process-induced, (b) stress-induced traps. Emission of a hole from the trap, corresponding to capture of a bonded electron from the silicon channel results in a larger increase in the system entropy for process-induced traps.              |

| Fig. 5. 15 Change in entropy $\Delta S/k_B$ for representative $V_{GS}$ values as a function of stressing time $t_s$ 73                                                                                                                        |

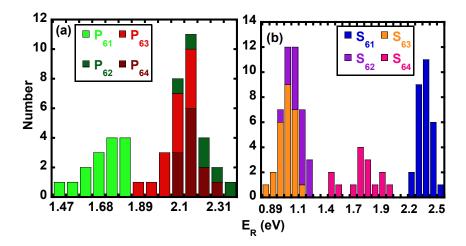

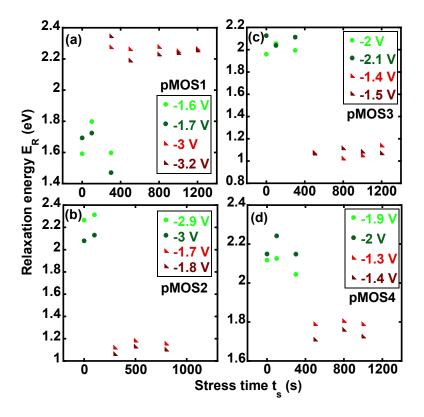

| Fig. 5. 16 Distribution of relaxation energy $E_R$ under stressing time instances for the (a) process-induced,                                                                                                                                 |

| (b) stress-induced traps                                                                                                                                                                                                                       |

| Fig. 5. 17 Calculated relaxation energy $E_R$ as a function of stressing time $t_s$ for representative $V_{GS}$ values.                                                                                                                        |

| The structural relaxation the defect undergoes when it emits a hole, i.e., captures an electron from the valence band, for the stress-induced defects in pMOS2 and pMOS3 is clearly much less than the other                                   |

| traps                                                                                                                                                                                                                                          |

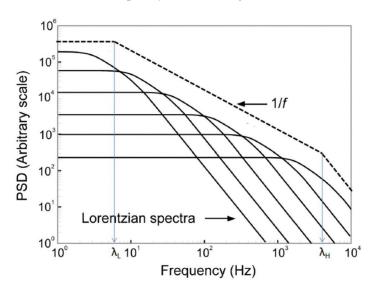

| Fig. 6. 1 $1/f$ noise power spectral density (PSD) as a function of frequency $f$ . Lorentzians from RTSs                                                                                                                                      |

| with different corner frequencies added up to produce the 1/f noise PSD. $\lambda_L$ and $\lambda_H$ are the corner                                                                                                                            |

| frequencies of the slowest and fastest traps, respectively [111]. (Reprinted with permission. Copyright $\bigcirc$ 2015, IEEE)                                                                                                                 |

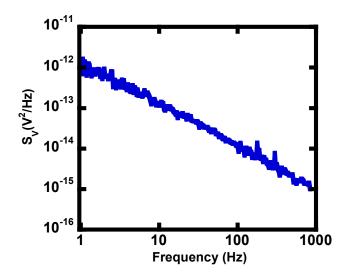

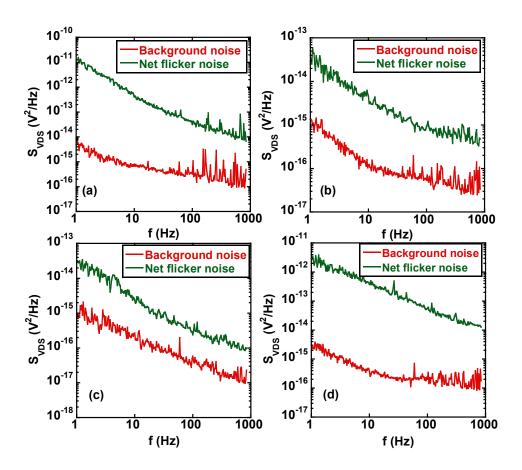

| Fig. 6. 2 Background noise and flicker (1/f) noise PSD as function of frequency $f$ for (a) $W \times L = 10 \times 1$                                                                                                                         |

| $\mu$ m <sup>2</sup> from x2388, (b) $W \times L = 10 \times 10 \ \mu$ m <sup>2</sup> from x2388, (c) $W \times L = 20 \times 4 \ \mu$ m <sup>2</sup> from x2396, and (d) $W \times L = 5 \times 10 \ \mu$ m <sup>2</sup> from x2550           |

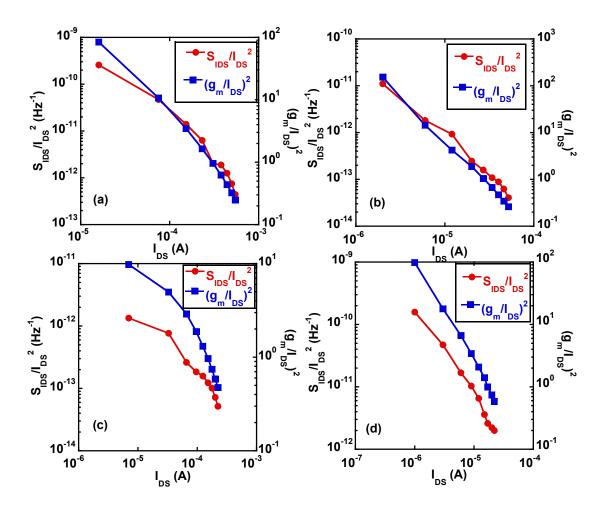

| Fig. 6. 3 Current noise PSD and $(g_m/I_{DS})^2$ as function of $I_{DS}$ for (a) $W \times L = 10 \times 1 \mu\text{m}^2$ from x2388, (b)                                                                                                      |

| $W \times L = 10 \times 10 \ \mu\text{m}^2 \text{ from x} \times 2388, \text{ (c)} \ W \times L = 20 \times 4 \ \mu\text{m}^2 \text{ from x} \times 2396, \text{ (d)} \ W \times L = 5 \times 10 \ \mu\text{m}^2 \text{ from x} \times 255081$ |

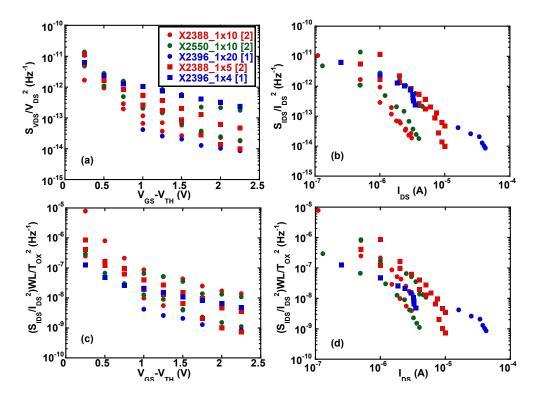

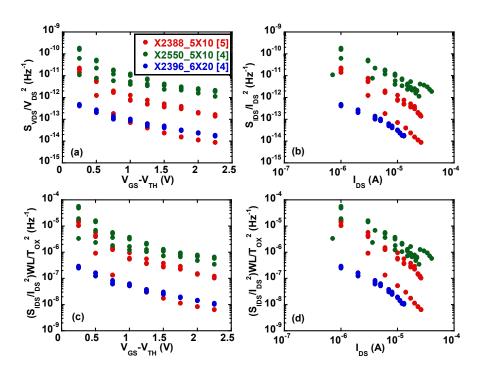

| Fig. 6. 4 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise                                                                                                                                           |

| PSD from $W \times L = 1 \times 10$ , $1 \times 5 \mu m^2$ of x2388, $W \times L = 1 \times 10 \mu m^2$ of x2550, and $W \times L = 1 \times 20$ , $1 \times 4 \mu m^2$ of                                                                     |

| x2396. The number inside the bracket stands for the numbers of nMOSFETs used for that device                                                                                                                                                   |

| dimension83                                                                                                                                                                                                                                    |

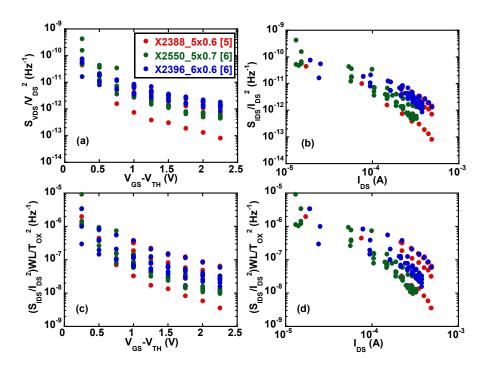

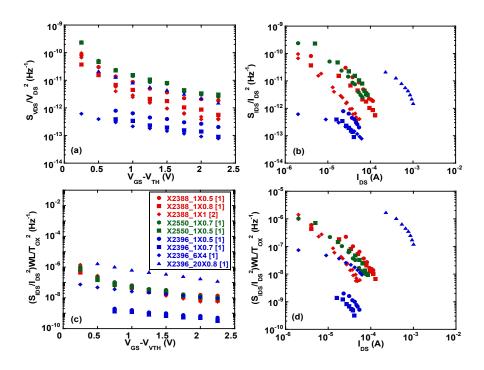

| Fig. 6. 5 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise                                                                                                                                           |

| PSD from $W \times L = 5 \times 0.6 \mu\text{m}^2$ of x2388, $W \times L = 5 \times 0.7 \mu\text{m}^2$ of x2550, and $W \times L = 6 \times 0.6 \mu\text{m}^2$ of x239683                                                                      |

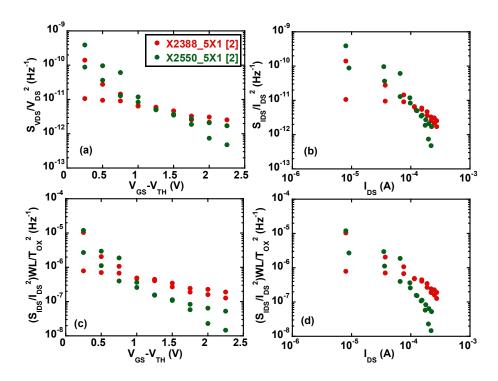

| Fig. 6. 6 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise PSD from $W \times L = 5 \times 1 \ \mu\text{m}^2$ of x2388 and $W \times L = 5 \times 1 \ \mu\text{m}^2$ of x2550                        |

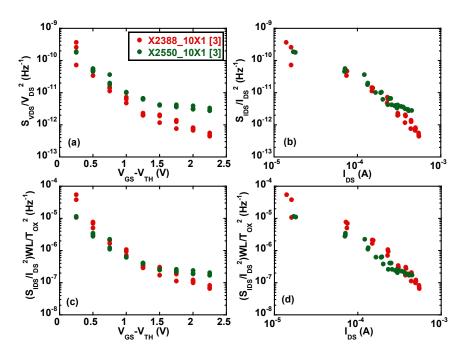

| Fig. 6. 7 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise                                                                                                                                           |

| PSD from $W \times L = 10 \times 1 \mu \text{m}^2$ of x2388 and $W \times L = 10 \times 1 \mu \text{m}^2$ of x2550                                                                                                                             |

| Fig. 6. 8 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise                                                                                                                                           |

| PSD from $W \times L = 5 \times 10 \ \mu\text{m}^2$ of x2388, $W \times L = 5 \times 10 \ \mu\text{m}^2$ of x2550, and $W \times L = 6 \times 20 \ \mu\text{m}^2$ of x2396 85                                                                  |

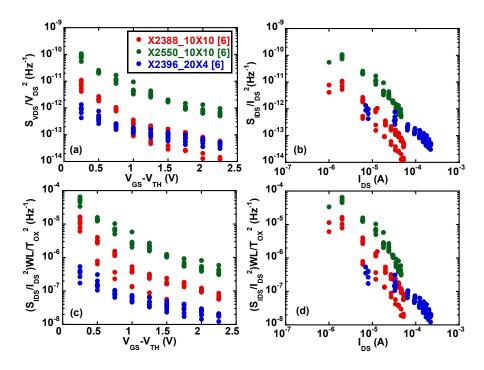

| Fig. 6. 9 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise PSD from $W \times L = 10 \times 10 \ \mu\text{m}^2$ of x2388, $W \times L = 10 \times 10 \ \mu\text{m}^2$ of x2550, and $W \times L = 20 \times 4 \ \mu\text{m}^2$ of x2396 85 Fig. 6. 10 Comparing (a) voltage noise PSD, (b) current noise PSD, (c) & (d) normalized current noise PSD from $W \times L = 1 \times 0.5 \ \mu\text{m}^2$ , $W \times L = 1 \times 0.8 \ \mu\text{m}^2$ and $W \times L = 1 \times 1 \times 10.8 \ \mu\text{m}^2$ of x2388, $W \times L = 1 \times 0.5 \ \mu\text{m}^2$ and | 5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $W \times L = 1 \times 0.7 \ \mu\text{m}^2 \text{ of } x2550, \text{ and } W \times L = 1 \times 0.5 \ \mu\text{m}^2, \ W \times L = 1 \times 0.7 \ \mu\text{m}^2, \ W \times L = 6 \times 4 \ \mu\text{m}^2, \text{ and } W \times L = 1 \times 0.7 \ \mu\text{m}^2$                                                                                                                                                                                                                                                                                                                                             |   |

| = $20 \times 0.8 \ \mu\text{m}^2 \text{ of } x2396.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5 |

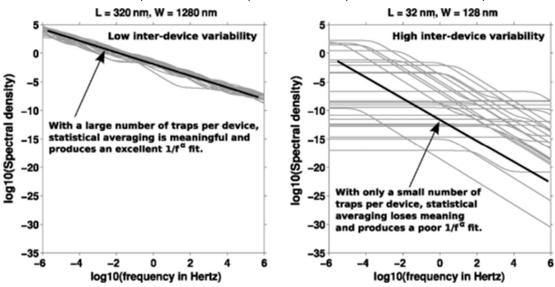

| Fig. 6. 11 Comparison of variability in devices with different sizes [113]. (Reprinted with permission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |

| Copyright © 2013, IEEE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 |

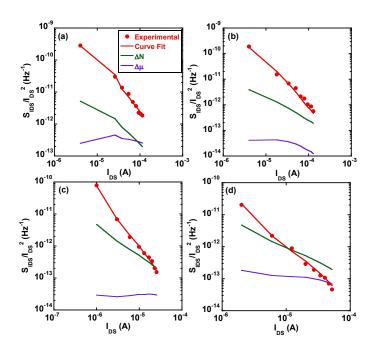

| Fig. 6. 12 Normalized 1/f current noise PSD data from the experiments, Curve fitted 1/f noise PSD data, number, and mobility fluctuations in x2388 nMOSFETs from (a) $W \times L = (1 \times 0.5) \mu m^2$ , (b) $W \times L = (1 \times 0.8)$                                                                                                                                                                                                                                                                                                                                                                    |   |

| $\mu$ m <sup>2</sup> , (c) W×L=(5×10) $\mu$ m <sup>2</sup> , and (d) W×L=(10×10) $\mu$ m <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9 |

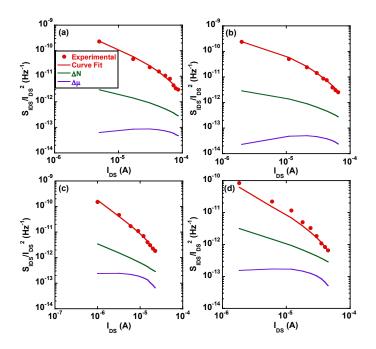

| Fig. 6. 13 Normalized 1/f current noise PSD data from the experiments, Curve fitted 1/f noise PSD data, number, and mobility fluctuations in x2550 nMOSFETs from (a) W×L=(1×0.5) $\mu$ m <sup>2</sup> , (b) W×L=(1×0.7)                                                                                                                                                                                                                                                                                                                                                                                           |   |

| $\mu$ m <sup>2</sup> , (c) W×L=(5×10) $\mu$ m <sup>2</sup> , and (d) W×L=(10×10) $\mu$ m <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9 |

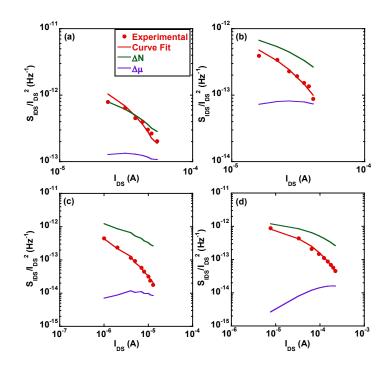

| Fig. 6. 14 Normalized 1/f current noise PSD data from the experiments, Curve fitted 1/f noise PSD data, number, and mobility fluctuations in x2396 nMOSFETs from (a) $W \times L = (1 \times 0.5) \mu m^2$ , (b) $W \times L = (1 \times 0.7)$                                                                                                                                                                                                                                                                                                                                                                    |   |

| $\mu$ m <sup>2</sup> , (c) W×L=(6×20) $\mu$ m <sup>2</sup> , and (d) W×L=(20×4) $\mu$ m <sup>2</sup> 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 |

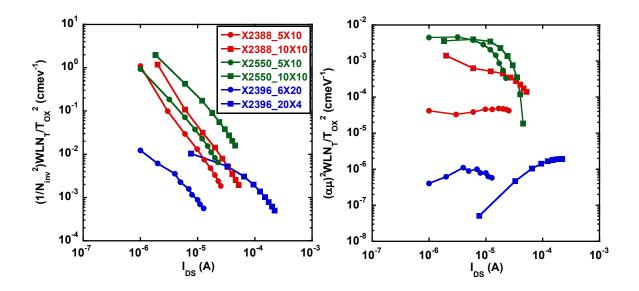

| Fig. 6. 15 Comparison of normalized (a) number and (b) mobility fluctuations as a function of $I_{DS}$ for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

| different dimensions of devices across the wafers. The dimensions of the wafers are: x2388, x2550                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |

| $(W \times L = 5 \mu m \times 10 \mu m, 10 \mu m \times 10 \mu m)$ , and $x = 2396 (W \times L = 6 \mu m \times 20 \mu m, 20 \mu m \times 4 \mu m)$ 91                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 |

# **List of Tables**

| Table 4. 1: Trap summary                                                                                              | 47       |

|-----------------------------------------------------------------------------------------------------------------------|----------|

| Table 5. 1: Extracted trap properties                                                                                 |          |

| Table 5. 2 : Defect Candidates                                                                                        |          |

| Table 6. 1: Device information from the three different wafers for 1/f noise measurements                             | 78       |

| Table 6. 2 : Obtained values of $N_T$ , $\alpha_0$ , and $\alpha_1$ for different wafers from numerical techniques of | f curve  |

| fitting. Bracket beside (W×L) denotes numbers of devices used for averaging current noise PSD                         | from our |

| measurements                                                                                                          | 90       |

#### **List of Symbols**

b Variation parameter used in Stern-Howard wavefunction (cm<sup>-1</sup>)

c Screening parameter of hole (m<sup>-1</sup>)

$C_{GC}$  Gate-channel capacitance (F/cm<sup>2</sup>)

$C_{GC}$  Corrected gate-channel capacitance (F/cm<sup>2</sup>)

$C_{GC}$  Gate-channel capacitance in the inversion region (F/cm<sup>2</sup>)

$C_{GC_{\alpha\nu}}$  Gate-channel overlap capacitance in the accumulation region (F/cm<sup>2</sup>)

$c_{hh}$  Screening parameter of heavy hole (m<sup>-1</sup>)

$C_{lh}$  Screening parameter of light hole (m<sup>-1</sup>)

$C_{OX}$  Oxide charge capacitance (F/cm<sup>2</sup>)

$d_{v}$  Valley degeneracy factor

Energy of an electronic level (eV)

$E_C$  Si conduction band edge (eV)

$E_D$  Donor energy level (eV)

$E_F$  Fermi energy level (eV)

$E_{g}$  Bandgap of Si (eV)

$E_p$  Energy where  $Eg(E)_{2D} f_p(E)$  peaks (eV)

$E_R$  Relaxation energy (eV)

$E_s$  Energy level of state S (eV)

$E_{\scriptscriptstyle T}$  Trap energy level (eV)

$E_{T}-E_{V_{CV}}$  Trap energy level with respect to the oxide valence band edge (eV)

$E_{V}$  Si valence band edge (eV)

$E_{V_{ov}}$  Oxide valence band edge (eV)

$E_{VS}$  Valence band maximum in Si (eV)

$E_{..}$  Electric field along the channel (V/cm)

$E_0$  First allowed quantized energy level of Si valence band (eV)

E' Oxide valence band bending along the trap position (eV)

| E''                        | Difference of the energy level between Fermi energy level and Si valence band at the Si-                           |

|----------------------------|--------------------------------------------------------------------------------------------------------------------|

|                            | SiO <sub>2</sub> interface (eV)                                                                                    |

| f                          | Frequency (Hz)                                                                                                     |

| $f_e$                      | Probability of a defect site being filled with an electron                                                         |

| $f_h$                      | Probability of a defect site being filled with a hole                                                              |

| $F_n$                      | Total number of switching events in one bin                                                                        |

| $f_p(E)$                   | Fermi-Dirac hole distribution function                                                                             |

| $F_s$                      | Surface electric field (V/m)                                                                                       |

| $f_{T}(E)$                 | Fermi-Dirac probability distribution function for electron                                                         |

| g                          | Trap degeneracy factor                                                                                             |

| $g(E)_{2D}$                | Two-dimensional density of states (cm <sup>-2</sup> )                                                              |

| $g_d$                      | MOSFET channel output conductance (A/V)                                                                            |

| $oldsymbol{g}_{do}$        | Degeneracy factor of donor                                                                                         |

| $g_{e}ig(N_{0_{OX}}ig)$    | Generation rate of the oxide charges in the equilibrium condition (s <sup>-1</sup> )                               |

| $g_e(N_{OX})$              | Generation rate of the oxide charges (s <sup>-1</sup> )                                                            |

| $g_{\scriptscriptstyle m}$ | MOSFET channel transconductance $(\Omega^{-1})$                                                                    |

| h                          | Planck's constant (Js)                                                                                             |

| I                          | Current (A)                                                                                                        |

| $I_{DS}$                   | Drain-source current (A)                                                                                           |

| k                          | Lattice co-ordinate (ev <sup>1/2</sup> kg <sup>-1/2</sup> rad <sup>-1</sup> s)                                     |

| $k_{\scriptscriptstyle B}$ | Boltzmann's constant (JK <sup>-1</sup> )                                                                           |

| $k_c$                      | Lattice co-ordinate at the intersection of two energy curves (defect site filled with a hole                       |

|                            | and empty of a hole) (ev <sup>1/2</sup> kg <sup>-1/2</sup> rad <sup>-1</sup> s)                                    |

| $k_1$                      | Lattice co-ordinate when the trap is empty of a hole (ev <sup>1/2</sup> kg <sup>-1/2</sup> rad <sup>-1</sup> s)    |

| $k_2$                      | Lattice co-ordinate when the trap is filled with a hole (ev <sup>1/2</sup> kg <sup>-1/2</sup> rad <sup>-1</sup> s) |

| $K_{1/f}$                  | Constant used in the Hooge's flicker noise model                                                                   |

| L                          | Channel length of the device (cm)                                                                                  |

| $L_{\scriptscriptstyle D}$ | Debye length (nm)                                                                                                  |

| $L_{\it eff}$              | Effective channel length of the device (cm)                                                                        |

| $m^*$                       | Conductivity effective mass of hole (kg)                                                              |

|-----------------------------|-------------------------------------------------------------------------------------------------------|

| $m_d^*$                     | Density of state effective mass of hole (kg)                                                          |

| $m_{dhh}^{st}$              | Density of state effective mass of heavy hole (kg)                                                    |

| $m_{dlh}^{st}$              | Density of state effective mass of light hole (kg)                                                    |

| $m_{hh}^*$                  | Conductivity effective mass of heavy hole (kg)                                                        |

| $m_{lh}^*$                  | Conductivity effective mass of light hole (kg)                                                        |

| $m_n^*$                     | Effective electron mass (kg)                                                                          |

| $m_p^*$                     | Effective hole mass (kg)                                                                              |

| $m_z^*$                     | Quantized effective mass of hole in z direction (kg)                                                  |

| n                           | Number of bins                                                                                        |

| N                           | Number of the particles in a state                                                                    |

| $N_C$                       | Effective density of states of electrons in the conduction band (cm <sup>-3</sup> )                   |

| $N_D$                       | Background donor doping concentration (cm <sup>-3</sup> )                                             |

| $n_i$                       | Intrinsic carrier concentration at equilibrium (cm <sup>-3</sup> )                                    |

| $N_{inv}$                   | Inversion layer channel electron density of a nMOSFET (cm <sup>-2</sup> )                             |

| $N_{\scriptscriptstyle OX}$ | Total number of trapped oxide charges                                                                 |

| $N_{0_{O\!X}}$              | Number of trapped oxide charges in equilibrium condition                                              |

| $N_{t}$                     | Trap density in a nMOSFET per unit area (cm <sup>-2</sup> )                                           |

| $N_{\scriptscriptstyle T}$  | Volume density of the traps per unit energy in the nMOSFET (cm <sup>-3</sup> eV <sup>-1</sup> )       |

| $N_T(E,x,y,z)$              | Distributions of the traps in the gate dielectric of the nMOSFET (cm <sup>-3</sup> eV <sup>-1</sup> ) |

| $N_{_{V}}$                  | Effective density of states of holes in the valence band (cm <sup>-3</sup> )                          |

| $n_0$                       | Equilibrium electron concentration (cm <sup>-3</sup> )                                                |

| $N_D^+$                     | Ionized donor doping concentration (cm <sup>-3</sup> )                                                |

| p                           | Inversion layer hole density per unit volume in a pMOSFET (cm <sup>-3</sup> )                         |

| P                           | Probability of finding the system in a particular state                                               |

| $P_{inv}$                   | Inversion layer hole density in the pMOSFET (cm <sup>-2</sup> )                                       |

| $P_{invhh}$                 | Inversion layer heavy hole density of the pMOSFET (cm <sup>-2</sup> )                                 |

| $P_{invlh}$                 | Inversion layer light hole density of the pMOSFET (cm <sup>-2</sup> )                                 |

| $P_t$                                        | Trap density in a pMOSFET (cm <sup>-2</sup> )                                                                                               |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| $p_{_{\scriptscriptstyle V}}\!\left(z ight)$ | Modified valence band hole distribution due to two-dimensional modeling (cm <sup>-1</sup> )                                                 |

| $p_{\scriptscriptstyle 2D}$                  | Hole density for the two-dimensional case (cm <sup>-2</sup> )                                                                               |

| $p_0$                                        | Equilibrium hole concentration (cm <sup>-3</sup> )                                                                                          |

| q                                            | Electronic charge (C)                                                                                                                       |

| $Q_{\scriptscriptstyle D}$                   | Total depletion layer charge in MOSFET (Ccm <sup>-2</sup> )                                                                                 |

| $Q_f$                                        | Fixed positive oxide charge per unit area (Ccm <sup>-2</sup> )                                                                              |

| $Q_{inv}$                                    | Total inversion layer charges per unit area in the MOSFET (Ccm <sup>-2</sup> )                                                              |

| $Q_{OX}$                                     | Oxide charges per unit area in the MOSFET (Ccm <sup>-2</sup> )                                                                              |

| R                                            | Resistance of the conducting channel $(\Omega)$                                                                                             |

| r(E)                                         | The rate of transition per unit energy at energy $E$ (s <sup>-1</sup> eV <sup>-1</sup> )                                                    |

| $r_e(N_{OX})$                                | Recombination rate of the oxide charges(s <sup>-1</sup> )                                                                                   |

| $r_eig(N_{0_{OX}}ig)$                        | Recombination rate of the oxide charges in the equilibrium condition (s <sup>-1</sup> )                                                     |

| $S_{g_e}$                                    | Fourier transform of the randomness in the generation rate of the oxide charges (Hz)                                                        |

| $S_I$                                        | Current noise power spectral density (PSD) (A <sup>2</sup> /Hz)                                                                             |

| $S_{I_{DS}}$                                 | Power spectral density (PSD) due to the drain-source current noise (A <sup>2</sup> /Hz)                                                     |

| $S_{_{N}}$                                   | Power spectral density (PSD) of the generation-recombination noise due to carrier number fluctuations (Hz <sup>-1</sup> )                   |

| $S_{N_{OX}}$                                 | Power spectral density (PSD) due to the fluctuation in the number of oxide charges (Hz <sup>-1</sup> )                                      |

| $S_{\mathcal{Q}_{OX}}$                       | Power spectral density due to fluctuation in the amount of oxide charges (C <sup>2</sup> /Hz)                                               |

| $S_{r_e}$                                    | Fourier transform due to the randomness in the recombination rate of the oxide charges                                                      |

| $S_{\scriptscriptstyle V}$                   | (Hz) Voltage noise power spectral density (PSD) of the thermal noise (V <sup>2</sup> /Hz)                                                   |

| $S_{V_{DS}}$                                 | Drain-source voltage noise power spectral density (PSD) of the noise (V <sup>2</sup> /Hz)                                                   |

| $S_{V_{FB}}$                                 | Voltage noise power spectral density (PSD) due to the flat-band voltage (V²/Hz)                                                             |

| $S_{_{\Delta I_{DS}}}$                       | Power spectral density (PSD) due to the drain-source current fluctuations (A <sup>2</sup> /Hz)                                              |

| $S_{\Delta N_t}$                             | Power spectral density due to the fluctuation in the number of occupied traps in a small W $\Delta y$ area of a nMOSFET (Hz <sup>-1</sup> ) |

Time (s) t TTemperature (K) Time span of each bin (s)  $t_n$  $T_{OX}$ Oxide layer thickness (cm) Stressing time (s)  $t_{s}$  $U_{\mathit{empty}}$ Energy of the defect site when it is empty of a hole (eV) Energy of the defect site when it is full with a hole (eV)  $U_{full}$ Drain-source voltage (V)  $V_{DS}$ Flat-band voltage (V)  $V_{\it FB}$ Gate-source voltage (V)  $V_{GS}$ Band bending inside the oxide (V)  $V_{OX}$ Threshold voltage (V)  $V_{TH}$ WChannel width of the device (cm) Coordinate axis along the channel width (µm) x Coordinate axis along the channel length (µm) yCoordinate axis along the oxide depth from the Si-SiO<sub>2</sub> interface (nm) The grand partition function  $Z_{G}$ Trap position into the oxide from the Si-SiO<sub>2</sub> interface (nm)  $Z_T$ Coulomb screened scattering coefficient (Vs)  $\alpha$ Ghibaudo's screened scattering parameter (Vs/C)  $\alpha_{_{\varrho h}}$ Hooge's parameter  $\alpha_{\scriptscriptstyle H}$ Screened scattering coefficient from RTS measurements (Vs)  $\alpha_{m}$ Screened scattering coefficient from the theoretical two-dimensional modeling (Vs)  $\alpha_{t}$ Screened scattering coefficient from the theoretical two-dimensional modeling for heavy  $\alpha_{\scriptscriptstyle thh}$ hole (Vs) Screened scattering coefficient from the theoretical two-dimensional modeling for light  $\alpha_{\scriptscriptstyle tlh}$ hole (Vs) Fitting parameter of the screened scattering coefficient from the UNMF model (Vs)  $\alpha_{\scriptscriptstyle 0}$ Fitting parameter of the screened scattering coefficient from the UNMF model (negative in  $\alpha_{\scriptscriptstyle 1}$ magnitude) (Vs)

β Current exponent in the current noise PSD of the 1/f noise γ Frequency exponent in the current noise PSD of the 1/f noise Fluctuations in the number of inversion layer electrons in the small area  $W\Delta y$  of a  $\delta\Delta N_{inv}$ nMOSFET Fluctuations in the number of traps in the small area  $W\Delta y$  of a nMOSFET  $\delta\Delta N_{\star}$ Capture activation energy (eV)  $\Delta E_{R}$ Trap energy level with respect to Si valence band edge (eV)  $\Delta E_{TV}$ Energy difference between the valence band maximum and the first allowed quantized  $\Delta E_0$ energy state of hole (eV) Energy difference between the valence band maximum and the first allowed quantized  $\Delta E_{0hh}$ energy state of heavy hole (eV) Energy difference between the valence band maximum and the first allowed quantized  $\Delta E_{0lh}$ energy state of light hole (eV)  $\Delta G$ Gibbs free energy (eV) Randomness in the generation rate of the oxide charges (s<sup>-1</sup>)  $\Delta g_{e}(t)$ Change in enthalpy (eV)  $\Delta H$ Difference between the upper and lower levels of current in a random telegraph signal  $\Delta I$ (RTS)(A)Fluctuations in the drain-source current in a small area (A)  $\delta I_{DS}$ Drain-source current fluctuations (A)  $\Delta I_{DS}$ Fluctuation in the number of carriers due to trapping/detrapping event  $\Delta N$ Mean square value of the fluctuation in the number of carriers  $\Delta \overline{N^2}$  $\Delta N_{inv}$ Number of inversion layer electrons in the small  $W\Delta y$  area of a nMOSFET Excess number of oxide charges from equilibrium  $\Delta N_{OX}$ Mean square value of the excess number of oxide charges from equilibrium  $\Delta N_{OX}^2$  $\delta N_{t}$ Trap density fluctuations in the nMOSFET (cm<sup>-2</sup>) Number of traps in the small  $W\Delta y$  area of a nMOSFET  $\Delta N_{\star}$ Total number of inversion layer holes in a small area  $W\Delta y$  $\Delta P_{inv}$ Total number of traps in a small area  $W\Delta y$  of a pMOSFET  $\Delta P_{t}$ Fluctuations in the total number of inversion layer holes in a pMOSFET  $\partial \Delta P_{im}$

$\partial \Delta P_t$  Fluctuations in the total number of traps in a small area  $W \Delta y$  in a pMOSFET

$\delta Q_{OX}$  Fluctuations in the oxide charge density (Ccm<sup>-2</sup>)

$\Delta r_{\rho}(t)$  Randomness in the recombination rate of the oxide charges (s<sup>-1</sup>)

$\Delta S$  Contribution from the change of entropy in Gibbs free energy (eVK<sup>-1</sup>)

$\Delta S/k_B$  Change in entropy

$\Delta V_{DS}$  Drain-source voltage fluctuations (V)

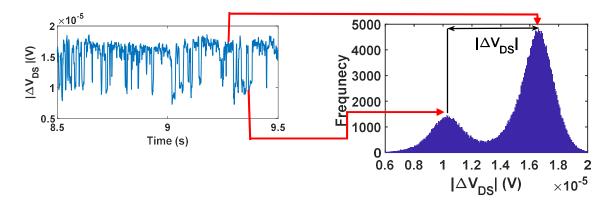

$|\Delta V_{DS}|$  RTS amplitude (V)

$\delta V_{FB}$  Fluctuations in the flat-band voltage (V)

$\delta V_{GS}$  Fluctuations in the gate-source voltage (V)

$\Delta y$  Small channel length (cm)

$\delta\mu$  Effective channel carrier mobility fluctuations (cm<sup>2</sup>/Vs)

$\varepsilon_{av}$  Average dielectric constant of Si and SiO<sub>2</sub>

$\varepsilon_0$  Permittivity of the free space (F/cm)

$\mathcal{E}_{Si}$  Dielectric constant of Si

$\varepsilon_{SiO_2}$  Dielectric constant of SiO<sub>2</sub>

$\zeta(z)$  Stern-Howard wavefunction (cm<sup>-1/2</sup>)

K Plane wave wave-vector (m<sup>-1</sup>)

$K_{hh}$  Plane wave wave-vector of heavy hole (m<sup>-1</sup>)

$\kappa_{lh}$  Plane wave wave-vector of light hole (m<sup>-1</sup>)

$\kappa'$  Final plane wave state wave vector (m<sup>-1</sup>)

$\lambda$  Electron wave attenuation coefficient (cm<sup>-1</sup>)

$\mu$  Effective channel carrier mobility in a MOSFET (cm<sup>2</sup>/Vs)

$\mu_{imp}$  Mobility due to impurity scattering (cm<sup>2</sup>/Vs)

$\mu_{lat}$  Mobility due to lattice scattering (cm<sup>2</sup>/Vs)

$\mu_{oth}$  Mobility except oxide charge scattering (cm<sup>2</sup>/Vs)

$\mu_{OX}$  Mobility limited by oxide charge scattering(cm<sup>2</sup>/Vs)

$\mu_t$  Mobility limited by oxide charge scattering in a two-dimensional mobility fluctuations

model (cm<sup>2</sup>/Vs)

$\sigma$  Trap capture cross-section (cm<sup>2</sup>)

| $\sigma_{_0}$                              | Capture cross-section pre-factor (cm <sup>2</sup> )                                                                   |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| $\overline{	au}$                           | Time constant of the transition of a signal between two levels (s)                                                    |

| $\overline{	au}_c$                         | Average capture time(s)                                                                                               |

| $\overline{	au}_e$                         | Average emission time (s)                                                                                             |

| $\overline{	au}_h$                         | Time constant of the higher level of a current signal RTS (s)                                                         |

| $\overline{	au}_l$                         | Time constant of the lower level of a current signal RTS (s)                                                          |

| $\overline{	au}_0$                         | Characteristic time constant (s)                                                                                      |

| $\overline{\mathcal{V}}_{th}$              | Average thermal velocity of holes (cms <sup>-1</sup> )                                                                |

| $\phi$                                     | Half of the angle between initial and final plane wave states                                                         |

| $oldsymbol{\phi}_{\!\scriptscriptstyle B}$ | Height of the tunneling barrier seen by the carriers at the Si-SiO <sub>2</sub> interface (eV)                        |

| $arphi_0$                                  | Energy difference between the valence band edges of Si and SiO <sub>2</sub> at the Si-SiO <sub>2</sub> interface (eV) |

| χ                                          | Degeneracy of a particular state                                                                                      |

| $\psi_s$                                   | Surface potential (eV)                                                                                                |

| $\omega$                                   | Lattice vibration frequency (rad/s)                                                                                   |

| $\hbar$                                    | Reduced Planck's constant (Js)                                                                                        |

#### **Chapter 1: Introduction**

#### 1.1 Background and Motivations Behind the Research Work

Downscaling the transistor dimensions over the last few decades following Moore's law has paved the way for rapid development in the CMOS technology. Miniaturization of the transistor size has led to higher operating speed, less amount of dissipated power, and cheaper manufacturing cost. It has inspired advancements in the information and data communication fields. However, since the device dimensions have become smaller, reliability issues have also been a concern from the circuit design perspective. Downsizing of the devices has introduced different types of noise like burst noise, random telegraph signal noise, and flicker noise. The presence of these unwelcoming noise components in the desired signal causes degradation of the device performance. To ensure higher reliability and to maintain proper operation of the device, minimizing the impact of noise is of great concern. Identifying the responsible defect centers for the noise component as well as the detailed examination of the defect properties can help us to ensure reliable operation of the device.

The very first appearance of the discrete switching behavior of the current through the semiconductor came from the detection of the burst noise. Burst noise was prominent in the reverse-biased Ge, Si junctions and tunnel diodes [1], [2]. This type of noise was supposed to originate from the surface effects, tunneling, and the random thermal fluctuation mechanisms [1], [2]. The distribution density functions for the pulse lengths of this noise followed an exponential law [2]. Burst noise was investigated in the forward-biased Si diodes and transistors under the active operating region as well as being incorporated in the equivalent circuits of the diode and transistor [3], [4]. This noise resulted from the current modulation through a defect when there was a charge state change of a generation-recombination site, positioned close to the defect center [4]. The time constants of the burst noise were also computed for the generation-recombination site [4].

However, the very first confirmation of the single carrier switching activities showing random telegraph signal (RTS) came from the work of Kandiah *et al.*, by conducting an experiment on electronic devices [5]. They implied that the Shockley-Read-Hall centers present in the Debye region (between the channel and fully depleted region) of the double gate four-terminal Si JFET were responsible for the low-frequency noise. Kandiah *et al.* later demonstrated that the charging/discharging of a single trap in the Debye region generated RTS [6]. On the electron emission from the defect site to the channel, the channel resistance was lowered and drain-source current increased [6]. Later, Ralls *et al.* investigated RTS for a comparatively smaller dimension device (0.1 μm²) in cryogenic temperatures [7]. They reported the exponential dependence of the time constants on temperature and voltage as well as calculating the corresponding

activation energies of the trap. The change of resistance was found to be consistent with the transfer of the channel carrier into the defect site. They implemented the mark space ratio to determine the trap position. Lattice distortion replaced quantum tunneling as the carrier capture mechanism in their work. Howard et al. later obtained a similar kind of result [8] to Ralls et al. [7], showing the temperature and bias voltage dependence of the capture and emission time constants for the traps. In addition, Howard et al. commented on the charge state of the defect site after an electron capture for the very first time [8]. After the capture of an electron, neutral or positively charged defect site became negatively charged or neutral, respectively, in that work [8]. Welland and Koch traced data related to RTS by utilizing the scanning tunneling microscope (STM) and found that this was consistent with the creation of the localized surface states [9]. The trapping of the carrier in the defect site led to the perturbation of the tunneling current in the vicinity of the site. With the increase of the gate voltage, time spent in the high current level decreased while time spent in the low current level was almost unaffected as reported by Uren et al. [10], [11], [12]. While capturing an electron, the negative electrostatic potential from the trapped charge increased the channel resistance, which led to the reduced capture time with biasing [12]. The capture and emission activities are believed to be taking place via a multi-phonon process. Later, in the works by Schulz et al., the multi phonon process was replaced by the utilization of the thermionic emission model while discussing the Coulomb repulsive centers [13]. They reported on the first observation of the individual attractive centers in pMOSFETs [14]. Shi et al. studied the impact of emission and capture of a trapped carrier on electron mobility [15]. They determined the trap's location along the channel from the difference between the forward and reverse bias mode and held discussions on the effect of electron heating on the capture cross-section of the trap and amplitude of the RTS.

Capture and emission activities by the individual defect sites were studied in detail by Kirton *et al.* [12]. They not only determined the capture and emission times but also the trap position from the interface, along with various RTS parameters, such as capture cross-section pre-factor, capture activation energy, relaxation energy, and change in enthalpy/ entropy. Multi-level switching in the output were observed for the nMOSFETs due to the presence of multiple traps at the same time. A four-level RTS resulting from three separate traps was reported by Amarasinghe *et al.* [16]. Influence from one of the traps over another one was observed to result in an energy level shift. For the trap positioned nearest to the interface, the computed screened scattering coefficient was the most sensitive to the gate voltage change. Later, traps placed deeper into the Si dioxide were studied in a separate work [17]. The effect of the Coulomb blockade was minimal due to the screening of the mobile charge carriers while operating the device in the strong inversion region, contrary to the weak inversion region. The two-dimensional mobility fluctuations model helps to understand the underlying physical mechanisms behind the screened Coulomb scattering between the inversion layer charge carriers and the trapped charge [18]. As the device size down-scaled, the channel

doping concentration was increased to prevent the punch-through effect and premature turn-on of the devices [19]. In high-doping density devices of small-scale dimensions, carrier motion is quantized to the perpendicular direction of the Si-SiO<sub>2</sub> interface [20], [21], [22]. Subsequently, electric sub-bands are present in the respective channel carrier energy bands for n- and pMOSFETs [21], [22]. As a result, two-dimensional quantum mechanical treatments were carried out for the small-scale devices in contrast to the classical three-dimensional treatments. Two-dimensional mobility fluctuations model was successfully implemented to calculate the mobility limited by the oxide charge scattering for nMOSFETs [22]. Screened Coulomb scattering coefficients were calculated from this model for both the interface and oxide traps in nMOSFETs [21], [22].

Recently, RTS has been a major source of concern for device reliability issues, especially for memory devices. The presence of RTS is an obstacle for performing read and write operations correctly in memory devices [23], [24]. In the dynamic random-access memory (DRAM) devices, the presence of multi-valued and metastable leakage currents has been reported to cause a failure in retaining the data for a specific hold time [25], [26]. The observation of the variable retention time ultimately led Yaney and Restle *et al.* to study RTS, which indicated the presence of a single defect in the depletion region. Resistance random access memory (RRAM) is gaining popularity nowadays because of the low cost of fabrication, fast read/write operation, low power consumption, and low threshold voltage [27]. However, in the path of development for RRAM, the presence of RTS in the RRAM current has caused reliability issues and affected memory stability [28]. Furthermore, RTS also provides information about the localized source of defects inside the active material. A significant amount of drain current fluctuation was observed during the read operation for the deeply scaled non-volatile memory devices [29]. Later, phase change memory devices were also studied to understand the impact of RTS [30].

Over the last few decades, the rapid downscaling of the device dimension has caused the reduction of the insulating oxide layer thickness, while the supply voltage has remained constant. As a result, there has been an increase in the vertical electric field in the oxide. Similarly, channel length scaling leads to a higher electric field in the channel. This increased channel electric field is responsible for the hot carrier effects in MOSFETs. During the hot carrier stressing, the carriers in the channel obtain higher kinetic energy to cause damages on the Si-SiO<sub>2</sub> interface and inside the SiO<sub>2</sub>. To identify the defect sites responsible for the damages by hot carrier stressing, studying RTS is of significant importance. Most of the publications have dealt with the effect of the hot carrier stressing on nMOSFETs [31], [32], [33]. There are different types of hot carrier stressing mechanisms such as the drain avalanche hot carrier (DAHC), channel hot carrier (CHC), and negative bias temperature instability (NBTI) stress. During DAHC stressing, the drain terminal of the MOSFET is biased at twice the voltage of the gate terminal. Both terminal voltages are above the

rated operating voltage of the device. While implementing NBTI, the PMOSFET is stressed at a high temperature range (80-150 degree C) and high negative voltage in the gate [34]. During CHC stressing, the gate and drain terminal of the MOSFET are biased at equal voltages above the rated operating condition. Due to the hot carrier stressing, degradation in several dc parameters such as drain current, gate current, threshold voltage, subthreshold slope, etc. has been observed [35], [36].

Comparing various stressing mechanisms, CHC stressing causes the worst degradation in pMOSFETs [37], [38], [39]. The smaller impact ionization rate of the carriers, as well as the higher Si-SiO<sub>2</sub> barrier, lead to lower amounts of degradation in pMOSFET than its nMOSFET counterpart [38]. Although being underreported, to ensure reliable operation of the pMOSFETs, much broader analyses are required to identify the responsible defect centers by examining the RTS parameters under CHC stressing. In the literature, a pioneering publication discussed the effect of DAHC stressing on nMOSFETs by analyzing the RTS data to determine trap position from the Si-SiO<sub>2</sub> interface and position of the trap energy level with respect to the conduction band edge of SiO<sub>2</sub> [40]. Fang et al. reported smaller time constants and closer trap position to the Si-SiO<sub>2</sub> interface while comparing the stress-induced traps with the process-induced traps [40]. A similar conclusion was rendered about the position of the trap under DAHC stressing from the works of Kang et al.; they also mentioned a lower value for the difference between the energy level of the trap to the edge of the conduction band for the process-induced ones [41]. The effect of DAHC stressing on the RTS amplitude has been scrutinized in the works of Simoen et al. for the process-induced traps [42], [43], [44]. Variation of the oxide and interface layer capacitance has been tied to the change of RTS amplitude for the MOSFETs in their notable work. However, additional publications are lacking information to determine whether the RTS amplitude would also be affected in similar ways for the stress-induced ones. Overall, CHC stressing needs to be explored in greater detail alongside the DAHC mechanism.

In most of the cases, not enough importance is given to identify the responsible defect center under the influence of different degradation mechanisms. The RTS parameters such as capture activation energy, relaxation energy, and trap energy level are helpful to gather information about the identification of the defect centers. Detailed investigations have been performed for the nMOSFETs [45], [46] alongside pMOSFETs [47] to identify the responsible defect centers under fresh conditions (no stressing mechanism taken into consideration).  $E'_{\delta}$  and  $E'_{\gamma}$  centers have been reported to be the major candidates for the defects in the pMOSFETs without any type of impact due to stressing [48], [49], [50], [51]. These  $E'_{\delta}$  and  $E'_{\gamma}$  centers were also viewed to be responsible behind flicker (1/f) noise in pMOSFETs [52]. One type of E' center (D-III Si) has also been identified to work as a defect center for the pMOSFETs [53], [54]. Furthermore, there have been some reports about the Hydrogen-related defects acting as a contender in the case of the stress-induced leakage currents (SILC) and NBTI [55], [56]. However, there is still a significant

knowledge gap due to the lack of examination of the CHC effects from the detailed study of the RTS trap parameters. The defect centers responsible behind the process and stress-induced traps need to be identified.

In this research work, RTS measurements were performed to study the effect of the CHC stressing on different RTS parameters at the room temperature for the pMOSFETs. The variable temperature measurements were also carried out to identify responsible defect centers. In the next chapters, we will proceed with these matters in detail. Chapter 2 includes the experimental setup required to take the RTS/ flicker noise measurements at/or below the room temperature. The definitions of different RTS parameters are explained in chapter 3. In chapter 4, discussions are carried out to study the effect of the CHC stressing on the room temperature RTS parameters. Chapter 5 includes elaborate discussions of the CHC effect on the variable temperature RTS parameters (such as activation energies, change in enthalpy/entropy) and the identification of the defect centers are undertaken. Chapter 6 covers a detailed study of the flicker noise data taken on available wafers from nMOSFETs of different technologies.

#### 1.2 Different Types of Electrical Noise

Noise is defined as an unwanted perturbation in the desired signal from a device. It represents the fluctuation of current and voltage in phase and magnitude from their average values. That random fluctuation integrated over a long time period results in no change from the average for stationary noise sources. There are two types of noise sources. External noise sources comprise noise from crosstalk between nearby circuits, interference from AC power lines, and electromagnetic signals. On the other hand, there are different types of internal noise including thermal noise, generation-recombination noise, random telegraph signal noise, and flicker noise. Defects positioned inside the bulk semiconductor oxide or at the oxide-semiconductor interface are responsible for the internal noise in the MOSFETs. Although it is impossible to eliminate the internal noise, its effect can be minimized by identifying and studying the physical properties of the defects as well as making necessary improvements in the fabrication process of the device.

#### 1.2.1 Thermal Noise