# Sub-10K Cold-Electron

# **Injection to Silicon at**

# **Room Temperature**

By

Ojas Tushar Bhayde

Presented to the faculty of the Graduate School of

## The University of Texas at Arlingtons

in Partial Fulfilment of the requirements

For the degree of

# MASTER OF SCIENCE

# THE UNIVERSITY OF TEXAS AT ARLINGTON

DECEMBER 2022

### **Acknowledgment**

I would like to thank my Research Advisor, Dr. Koh for his extremely valuable guidance, feedback and support without whom this research would not have been possible. I would like to thank my committee members, Dr. Koh, Dr. Cao, and Dr. Hao for their support and understanding in helping me to complete my thesis.

I would like to thank all my group members for their valuable support and feedback during discussions and help with my research experiment during the course of my thesis project.

I would also like to thank the Nanofab staff – Dennis, Kevin, Mick, and Dr. Hozabari for training me to use the various equipment in the Nanofab Research Centre which were crucial for my dissertation research. I would like to thank Dr. Jiang for his support in using TEM Images. I would like to thank Tyler Gish (Northwestern University), and Matthew (UTA).

This project is funded by NSF PREM (DMR-2122128), NSF (CMMI-1463451) and NSF RAPID (ECCS-2031770).

#### **Abstract**

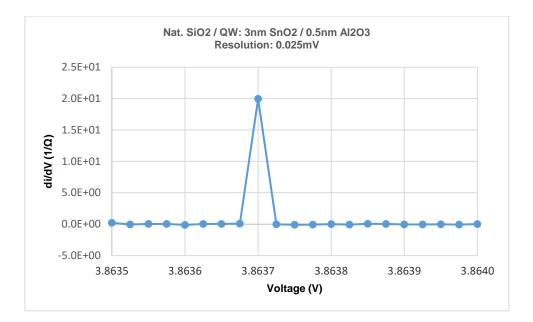

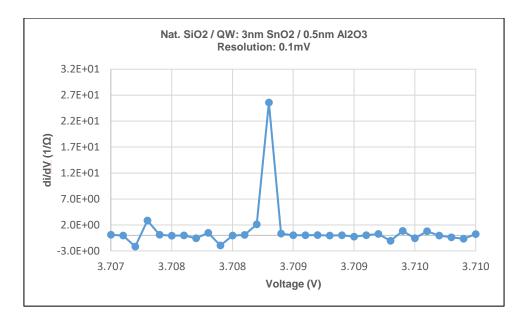

The Fermi-Dirac thermal excitation of electrons results in unwanted off-state leakage currents in metal-oxide-semiconductor field-effect transistors (MOSFETs), leading to excessive power consumption in modern electronic devices. The electron thermal excitation results in a theoretical subthreshold slope limit of 60 mV/decade at room temperature, which forces the devices to use a high supply voltage leading to high power consumption. This study investigates a new architecture capable of suppressing electron thermal excitation by using a quantum well (QW) as an energy filter. The QW energy filter is composed of a tunneling barrier 1 (0.5 to 1 nm Al<sub>2</sub>O<sub>3</sub> or 0.3-1 nm Si<sub>3</sub>N<sub>4</sub> or no tunneling barrier) a quantum well (QW) layer (3-5 nm tin oxide, SnO<sub>2</sub>), and a tunneling barrier 2 (native silicon dioxide, SiO<sub>2</sub>). The energy filter layers are sandwiched between a chromium electrode and silicon. This energy-filtering structure makes it possible to inject cold electrons into silicon with abrupt current jumps, which correspond to the alignment of the QW levels with the conduction band edge of silicon. Differential conductance (dl/dV) plots show extremely narrow peaks, with their FWHMs (full widths at half maximum) only 0.025mV, corresponding to an effective electron temperature of 0.08 Kelvin at room temperature. This cold electron injection to Si at room temperature has a potential to create transistors that operate with extremely little energy consumption.

# Table of Contents

| ACKNOWLEDGMENT                                                            | II  |

|---------------------------------------------------------------------------|-----|

| ABSTRACT                                                                  | 111 |

| TABLE OF CONTENTS                                                         | IV  |

| LIST OF FIGURES                                                           | VII |

| CHAPTER 1: INTRODUCTION                                                   | 1   |

| CHAPTER 2: ENERGY FILTERING PRINCIPLE                                     | 4   |

| 2.1 CONCEPT                                                               | 4   |

| 2.2 PRINCIPLE OF QUANTUM WELL AS ENERGY FILTER                            | 5   |

| CHAPTER 3: FABRICATION PROCEDURE                                          | 8   |

| 3.1 CHAPTER FABRICATION FOR QW-SI DEVICE                                  | 8   |

| 3.2 SUBSTRATE PREPARATION                                                 | 8   |

| 3.3 Thermal Oxide Growth                                                  | 9   |

| 3.4 DICING OF SILICON WAFERS WITH [111] CRYSTAL ORIENTATION AND CLEANING. | 12  |

| 3.5 PATTERING OF SILICON ISLAND REGION                                    | 13  |

| 3.5.1 Photolithography for silicon window pattern exposure                | 14  |

| 3.5.2 Reactive Ion Etching – Dry Etching                                  | 16  |

| 3.5.3 Lift-off of the photoresist                                         | 18  |

| 3.5.4 Sample Cleaning and Measurements                                    | 19  |

| 3.5.5 Wet Etching and Tunnelling Barrier 2                                | 19  |

| 3.6 PATTERNING OF SILICON CONTACT PAD.                                    | 21  |

| 3.6.1 Photolithography for silicon contact-pad pattern exposure           | 21  |

| 3.6.2 Reactive Ion Etching – Dry Etching                                      | . 23 |

|-------------------------------------------------------------------------------|------|

| 3.6.3 Lift-off of the photoresist.                                            | 24   |

| 3.6.4 Photolithography for overlapping silicon contact pad pattern exposure   | 24   |

| 3.6.5 Wet Etching of silicon dioxide                                          | . 26 |

| 3.6.6 Silicon Contact Metal Pad Deposition                                    | . 27 |

| 3.6.7 Lift-off of the photoresist                                             | . 29 |

| 3.6.8 RTA treatment to establish Ohmic contact                                | . 30 |

| 3.7 Building Energy Filter stack                                              | . 34 |

| 3.7.1 Quantum well layer deposition                                           | . 35 |

| 3.7.2 Tunneling Barrier 1 deposition                                          | . 37 |

| 3.8 SOURCE AND DRAIN CONTACT METAL PAD DEPOSITION.                            | . 38 |

| 3.8.1 Photolithography for overlapping silicon contact pad pattern exposure   | . 39 |

| 3.8.2 Source - Drain Contact Metal Pad Deposition                             | . 40 |

| 3.8.3 Lift-off of the photoresist                                             | . 42 |

| 3.9 RTA FOR MAKING QUANTUM WELL POLYCRYSTALLINE.                              | . 43 |

| 3.10 PASSIVATION LAYER DEPOSITION                                             | . 43 |

| 3.11 GOLD CONTACT METAL PAD DEPOSITION.                                       | . 44 |

| 3.11.1 Photolithography for overlapping silicon contact pad pattern exposure. | . 45 |

| 3.11.2 Via holes etching                                                      | . 46 |

| 3.11.3 Lift-off of the photoresist.                                           | . 48 |

| 3.11.4 Photolithography for overlapping silicon contact pad pattern exposure. | . 48 |

| 3.11.5 Gold Contact Metal Pad Deposition                                      | . 50 |

| 3.11.6 Lift-off of the photoresist.                                           | . 51 |

| CHAPTER 4: RESULT AND DISCUSSION                                              | . 52 |

| 4.1 ELECTRICAL CHARACTERIZATION                                               | 52   |

| R | REFERENCES                                                       | . 92 |

|---|------------------------------------------------------------------|------|

| C | CHAPTER 5: CONCLUSION                                            | . 91 |

|   | 4.8 EFFECT OF LOW TEMPERATURE FOR VARIOUS QUANTUM WELL THICKNESS | 83   |

|   | 4.7 EFFECT OF LOW TEMPERATURE                                    | 81   |

|   | 4.6 LOW CURRENT MEASUREMENT                                      | 79   |

|   | 4.5 VARIATION IN QW THICKNESS                                    | 72   |

|   | 4.4 VARIATION IN RTA TREATMENT                                   | 65   |

|   | 4.3 FIRST DEVICE WITH PROMISING RESULTS                          | 59   |

|   | 4.2 Ohmic Contact                                                | 55   |

#### List of figures

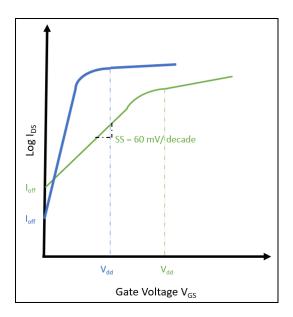

Figure 1: Subthreshold swing (green) limit at 300K. Blue IV shows desired slope to reduce Vdd and Off-state current

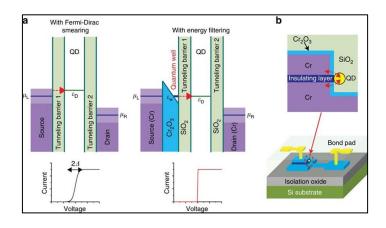

Figure 2: Energy filtering and cold-electron transport in double-barrier tunneling junction (DBTJ) structure

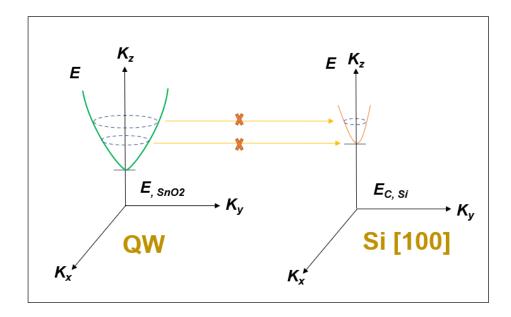

Figure 3: Schematic showing unaligned Quantum well and Silicon [100] bands structure

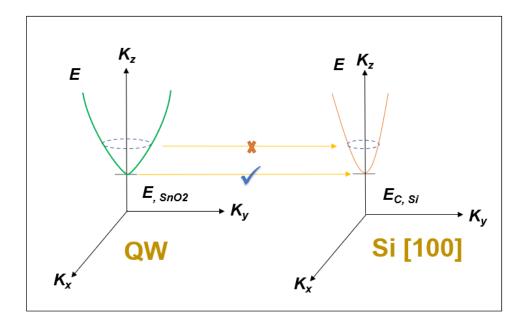

Figure 4: Schematic showing aligned Quantum well and Silicon [100] bands structure

Figure 5: Tystar Oxidation Furnace for Thermal Oxidation and nitride of Silicon

Figure 6: DISCO Automatic dicing saw for dicing the silicon wafers

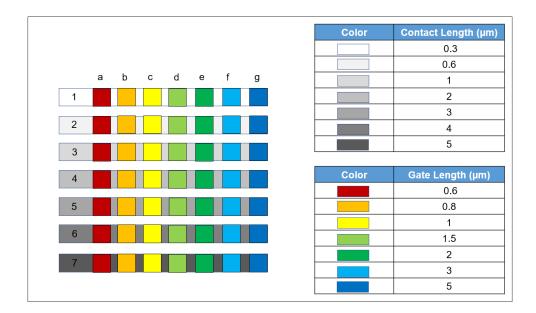

Figure 7: Mask layout showing variation in contact area and gate length

Figure 8: OAI Aligner Equipment for UV Photolithography

Figure 9: Technics Macro RIE – 8800 equipment for Reactive Ion Etching

Figure 10: KLA Tencor-P6 profilometer for profile measurement

Figure 11: Ellipsometer for measuring thickness of photoresist

Figure 12: AJA e-beam evaporator equipment for metal deposition

Figure 13: Homebuilt Sputter deposition equipment for DC and RF Sputter deposition

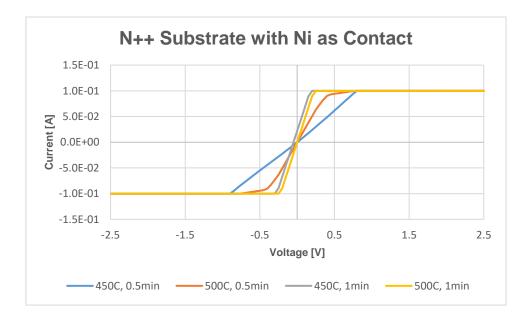

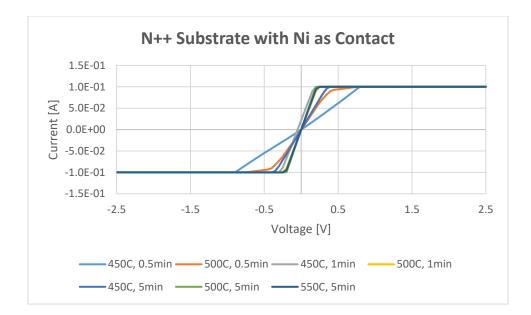

Figure 14: Si - Si IV showing Ohmic contact for N++Si contact with Ni as contact metal

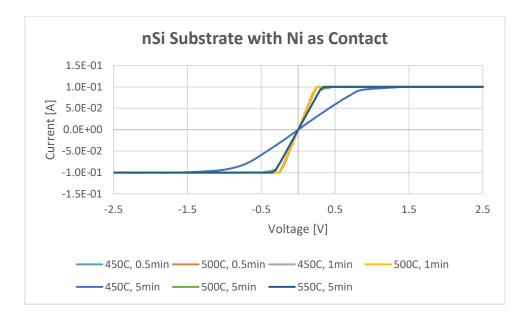

Figure 15: Si - Si IV showing Ohmic contact for n-Si contact with Ni as contact metal

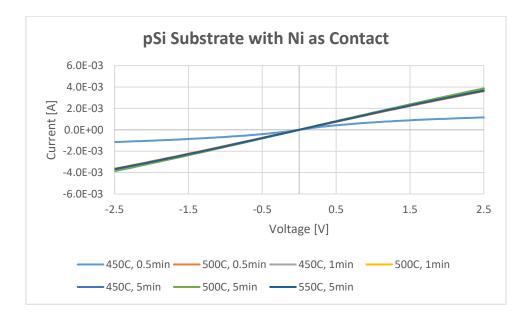

Figure 16: Si - Si IV showing Ohmic contact for p-Si contact with Ni as contact metal

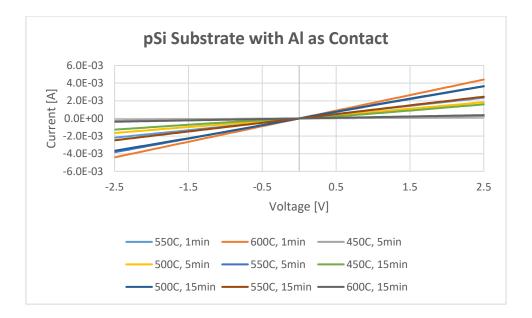

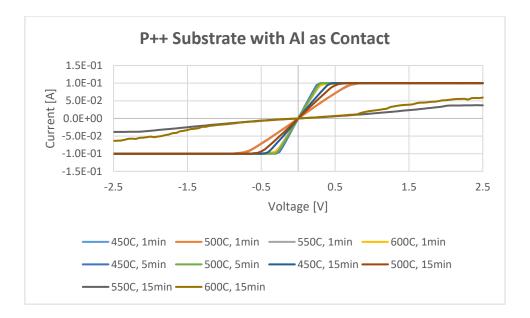

Figure 17: Si - Si IV showing Ohmic contact for p-Si contact with AI as contact metal

Figure 18: Si - Si IV showing Ohmic contact for P++Si contact with AI as contact metal

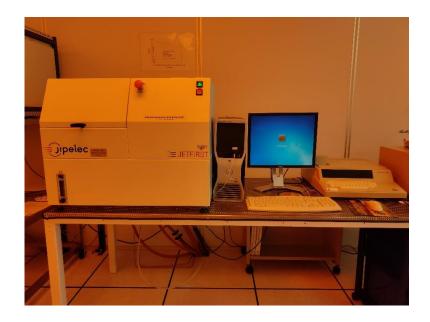

Figure 19: JetFirst Rapid Thermal Annealing for Heating samples

Figure 20: Ocean Optics Reflectometer for thickness measurement

Figure 21: CHA E-Beam Solution for metal deposition

Figure 22: Table of Various Metal work function

Figure 23: AJA Sputter Deposition equipment for DC and RF Sputtering

Figure 24: IV Probe station with Agilent 4155C equipment for IV measurement

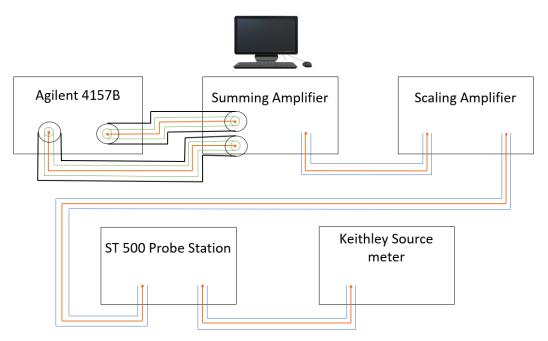

Figure 25: Wiring diagrams of IV measurement equipment

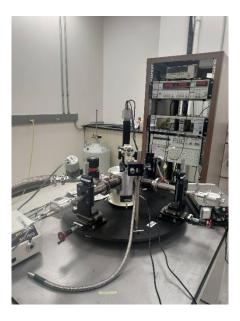

Figure 26: Current-voltage measurement setup for Vacuum measurement of devices

Figure 27: Si - Si IV showing Ohmic contact for N++Si contact with Ni as contact metal

Figure 28: Si - Si IV showing Ohmic contact for n-Si contact with Ni as contact metal

Figure 29: Si - Si IV showing Ohmic contact for p-Si contact with Ni as contact metal (Top) with AI as contact metal (bottom)

Figure 30: Si - Si IV showing Ohmic contact for P++Si contact with AI as contact metal

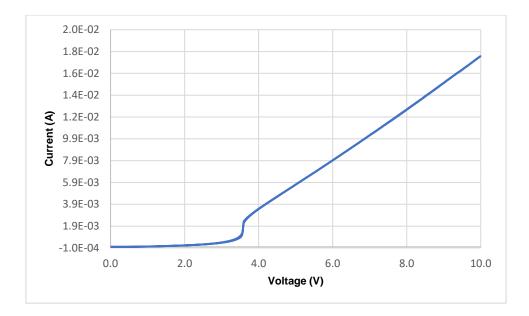

Figure 31: Source-Silicon IV through SnO<sub>2</sub> Quantum Well Energy filter (EF Stack consists of Native SiO<sub>2</sub>/QW: 1.5nm Sn heated at 200C-1 hr on a hot plate/ 0.5nm ALD deposited Al<sub>2</sub>O<sub>3</sub>)

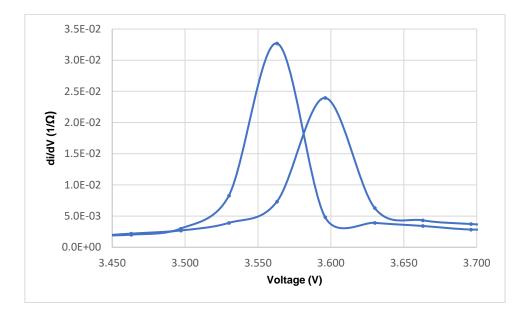

Figure 32: Differential conductance plot for Source-Silicon IV through SnO<sub>2</sub> Quantum Well Energy filter (EF Stack consists of Native SiO<sub>2</sub>/ QW: 1.5nm Sn heated at 200°C

-1hr on a hot plate/ 0.5nm ALD deposited  $Al_2O_3$ ) (Forward and reverse measurements show a peak shift of 10mV)

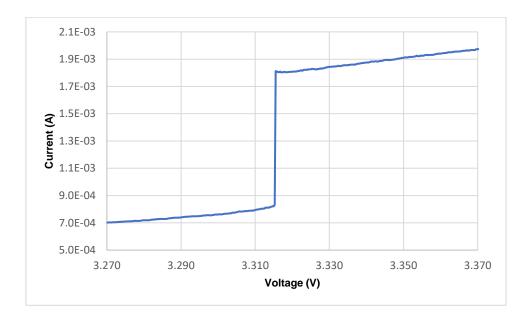

Figure 33: Source-Silicon IV through SnO<sub>2</sub> Quantum Well Energy filter

(EF Stack consists of Native SiO<sub>2</sub>/ QW: 1.5nm Sn heated at 200°C -1 hr on a hot

plate/ 0.5nm ALD deposited Al<sub>2</sub>O<sub>3</sub>)

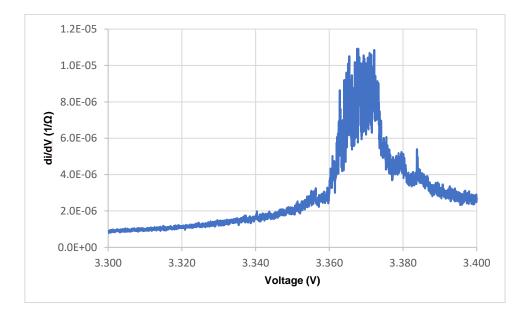

Figure 34: Lock-in Amplifier Differential Conductance vs Voltage measurements showing a FWHM of 10mV

Figure 35: TEM image showing Energy filter layer stack for 50nm Cr/ 0.3nm Si $_3N_4$ Native SiO<sub>2</sub>/ QW: 1.5nm Sn heated at 200°C -1 hr on a hot plate 0.5nm ALD deposited Al<sub>2</sub>O<sub>3</sub>

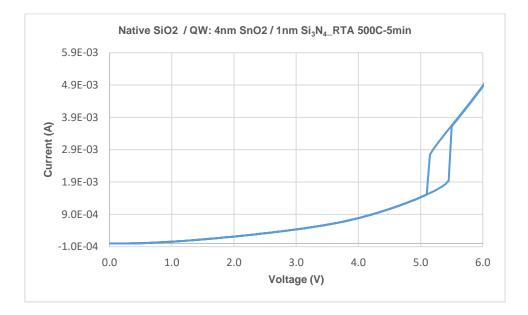

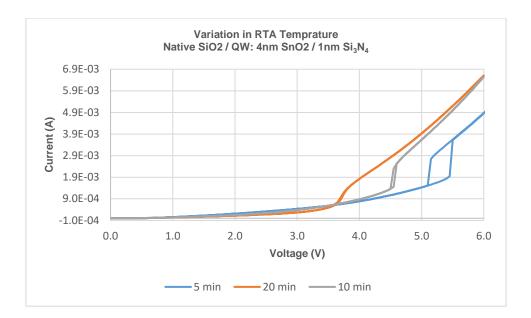

Figure 36: Source-Silicon IV for device with QW: 4nm SnO<sub>2</sub>, TB1: 1 nm Si<sub>3</sub>N<sub>4</sub> and RTA 500°C -5min

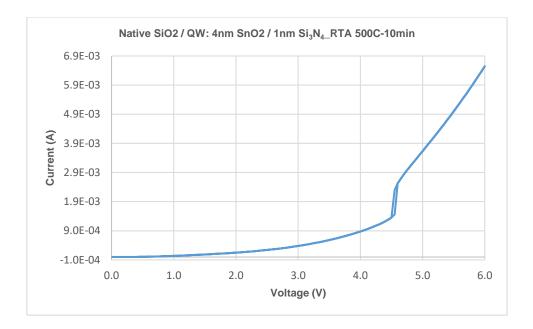

Figure 37: Source-Silicon IV for device with QW: 4nm SnO<sub>2</sub>, TB1: 1 nm Si<sub>3</sub>N<sub>4</sub> and RTA 500°C -10min

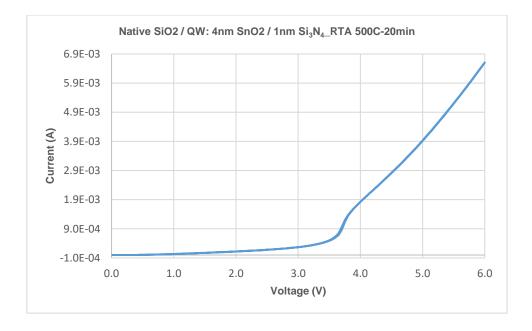

Figure 38: Source-Silicon IV for device with QW: 4nm SnO<sub>2</sub>, TB1: 1 nm Si<sub>3</sub>N<sub>4</sub> and RTA 500°C -20min

Figure 39: Source-Silicon IV showing variation of abrupt jump voltage with increased RTA annealing time

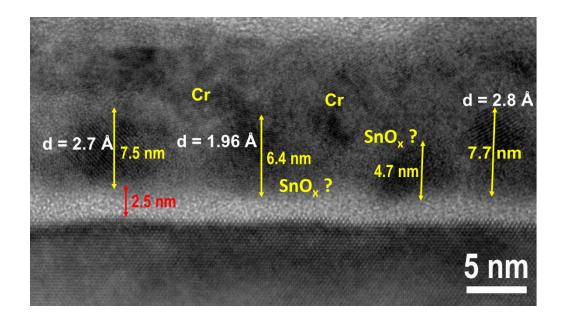

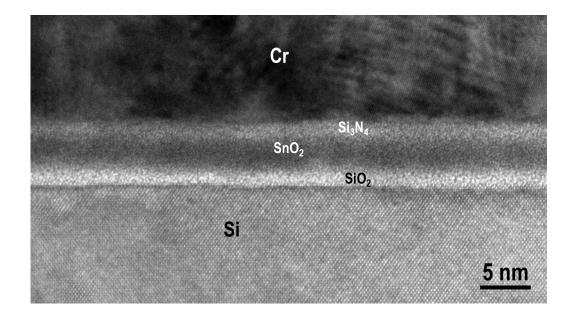

Figure 40: TEM image showing Energy filter layer stack for 50nm Cr/15nm Au/50nm Cr/1nm Si<sub>3</sub>N<sub>4</sub>/3nm SnOx/1nm SiO<sub>2</sub>/Si before RTA annealing

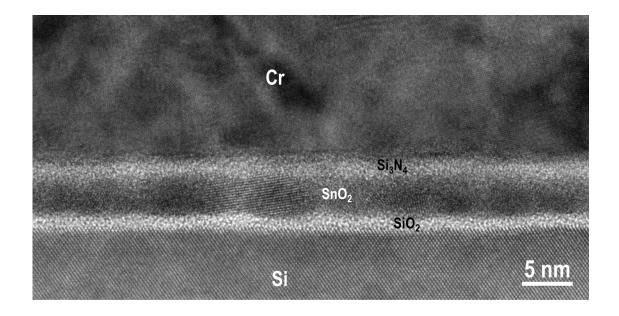

Figure 41: TEM image showing Energy filter layer stack for 50nm Cr/15nm Au/50nm Cr/1nm Si<sub>3</sub>N<sub>4</sub>/3nm SnOx/1nm SiO<sub>2</sub>/Si After RTA annealing at 500°C for 30 minutes

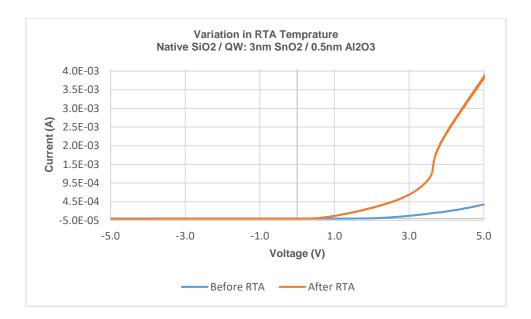

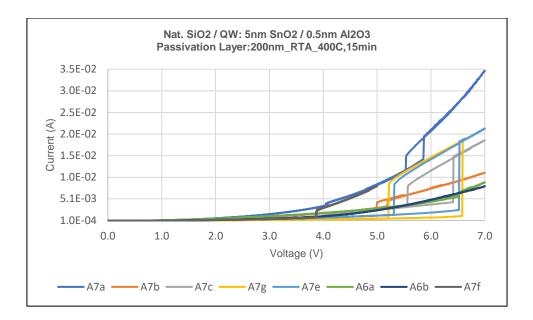

Figure 42: Effect of RTA treatment on Source-Silicon IV for device with QW: 3nm SnO<sub>2</sub>, TB1: 0.5nm Al<sub>2</sub>O<sub>3</sub> (RTA: 500°C, 15min)

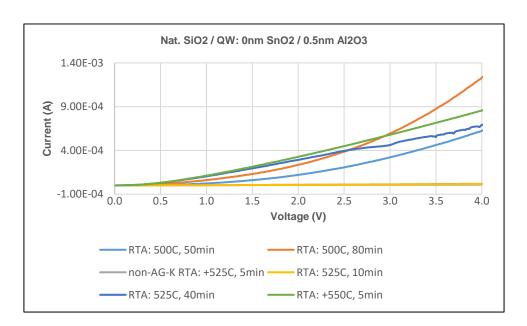

Figure 43: Effect of various RTA treatment on Source-Silicon IV for device with QW: 0nm SnO<sub>2</sub>, TB1: 0.5nm Al<sub>2</sub>O<sub>3</sub>

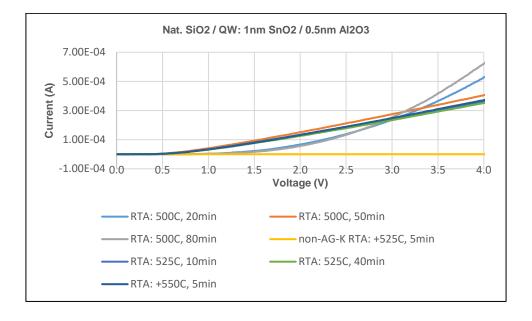

Figure 44: Effect of various RTA treatment on Source-Silicon IV for device with QW: 1nm SnO<sub>2</sub>, TB1: 0.5nm Al<sub>2</sub>O<sub>3</sub>

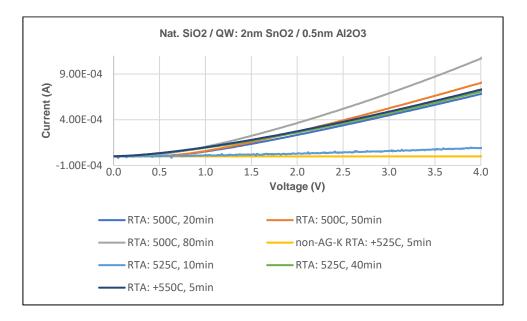

Figure 45: Effect of various RTA treatment on Source-Silicon IV for device with QW: 2nm SnO<sub>2</sub>, TB1: 0.5nm Al<sub>2</sub>O<sub>3</sub>

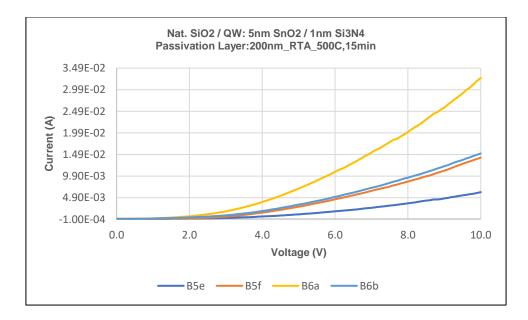

Figure 46: Effect of RTA treatment 500°C for 15 minutes on Source-Silicon IV for device with QW: 5nm SnO<sub>2</sub>, TB1: 1nm Si<sub>3</sub>N<sub>4</sub> with Passivation layer of 200nm SiO<sub>2</sub>

Figure 47: Effect of RTA treatment 400°C for 15 minutes on Source-Silicon IV for device with QW: 5nm SnO<sub>2</sub>, TB1: 1nm Si<sub>3</sub>N<sub>4</sub> with Passivation layer of 200nm SiO<sub>2</sub>

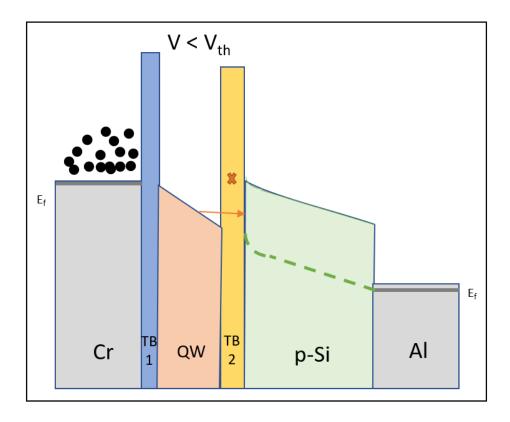

Figure 48: Energy Band diagram showing Electron transport through quantum well energy filter when a positive bias is applied ( $V < V_{th}$ )

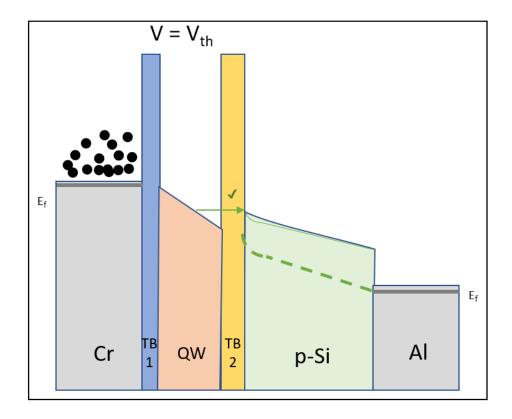

Figure 49: Energy Band diagram showing Electron transport through quantum well energy filter when a positive bias is applied ( $V = V_{th}$ )

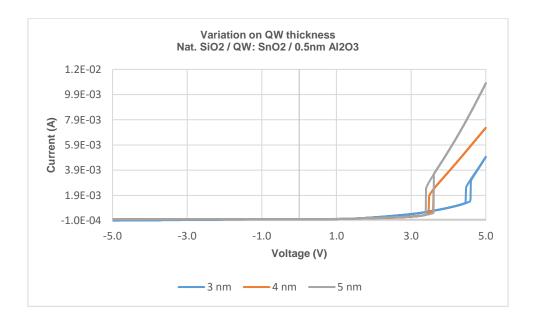

Figure 50: Effect of variation in QW thickness on Source-Silicon IV for device with TB2: Native Oxide SiO<sub>2</sub>, TB1: 0.5nm Al<sub>2</sub>O<sub>3</sub>

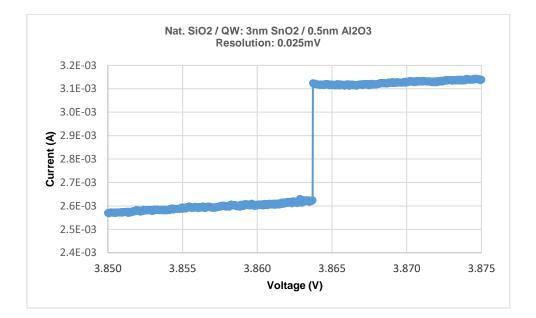

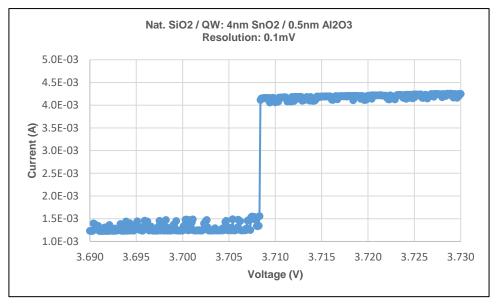

Figure 51: Source-Silicon IV for device (Top) and Differential Conductance vs Voltage (Bottom) for device with Native SiO<sub>2</sub> / QW: 3nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min Figure 52: Source-Silicon IV for device (Top) and Differential Conductance vs Voltage (Bottom) for device with Native SiO<sub>2</sub> / QW: 4nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

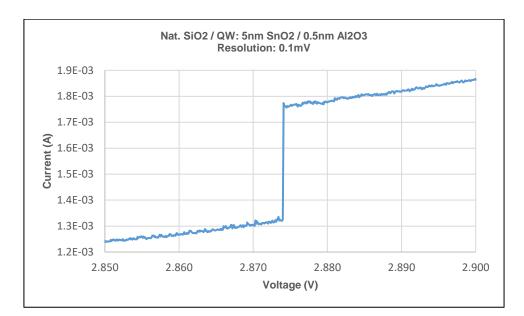

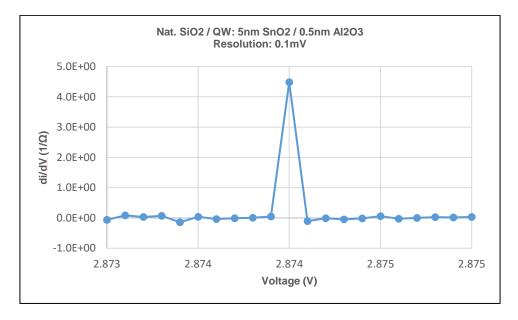

Figure 53: Source-Silicon IV for device (Top) and Differential Conductance vs Voltage (Bottom) for device with Native SiO<sub>2</sub> / QW: 5nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

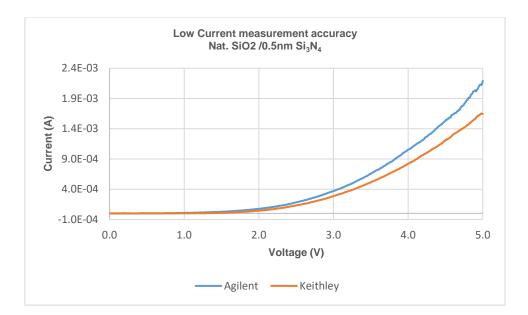

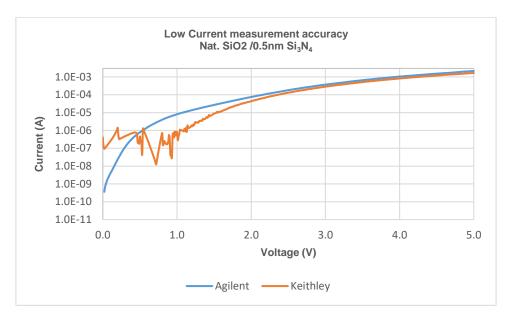

Figure 54: Effect of cables on accuracy in low current measurement (Top: In normal scale, Bottom: In Log scale)

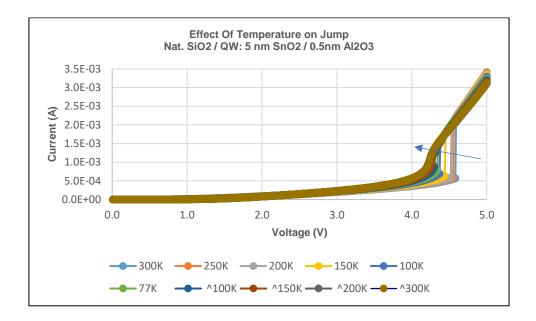

Figure 55: Effect of low temperature on the abrupt jump disappearing of Source-Silicon IV for device with Native SiO<sub>2</sub> / QW: 5nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C - 15min

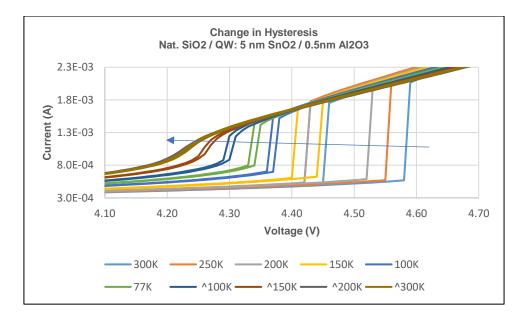

Figure 56: Effect of low temprature on the abrupt jump disappearing zoomed in of Source-Silicon IV for device with Native SiO<sub>2</sub> / QW:  $5nm SnO_2 / 0.5nm Al_2O_3_RTA$   $500^{\circ}C -15min$

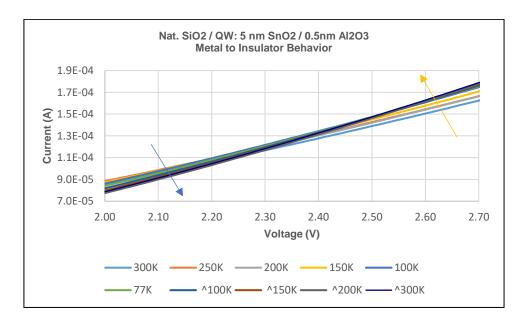

Figure 57: Effect of low temprature on the Source-Silicon Iv showing metal to insulator behavior for device with Native  $SiO_2 / QW$ : 5nm  $SnO_2 / 0.5nm Al_2O_3$ \_RTA 500°C -15min

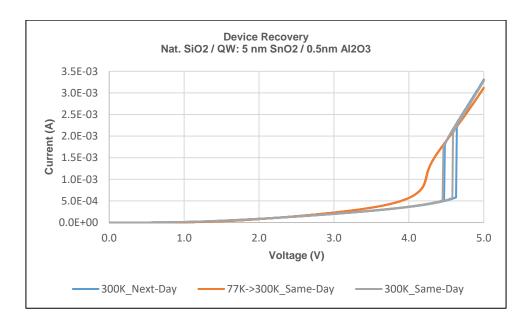

Figure 58: Device recovery effect on the Source-Silicon IV showing recovery of abrupt jump for device with Native SiO<sub>2</sub> / QW: 5nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

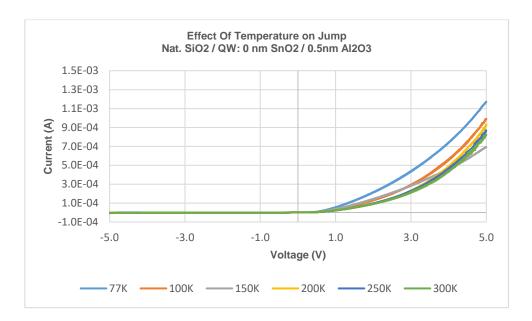

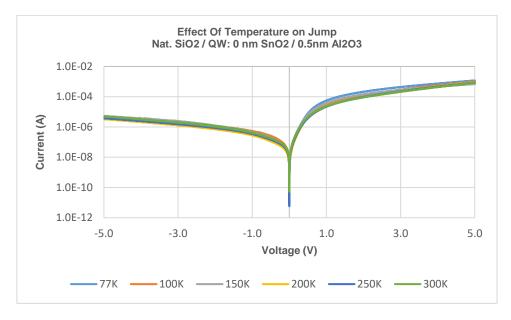

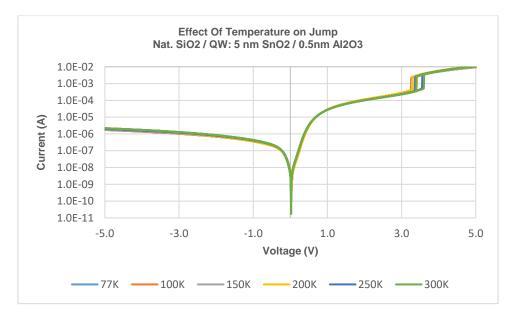

Figure 59: Effect of various low temprature of Source-Silicon IV (Top: In normal scale, Bottom: In Log scale) for device with Native SiO<sub>2</sub> / QW: 0nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

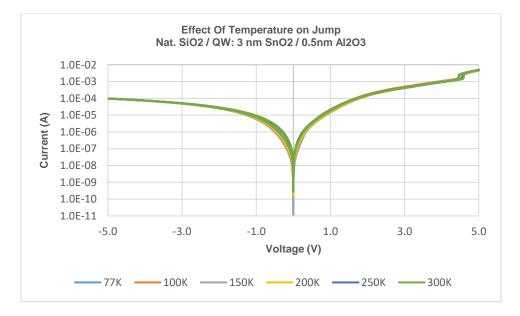

XI

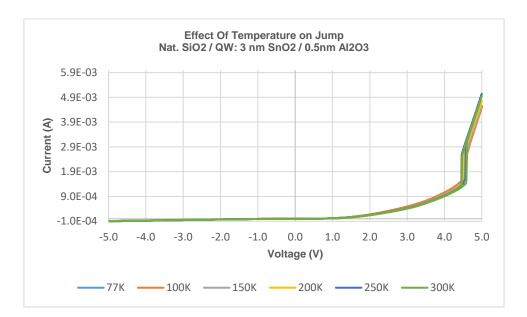

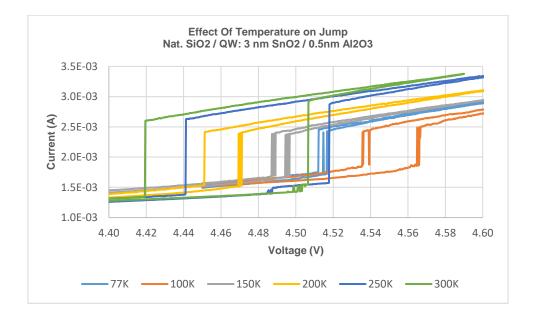

Figure 60: Effect of various low temprature of Source-Silicon IV (Top: In normal scale, Bottom: In Log scale) for device with Native SiO<sub>2</sub> / QW: 3nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

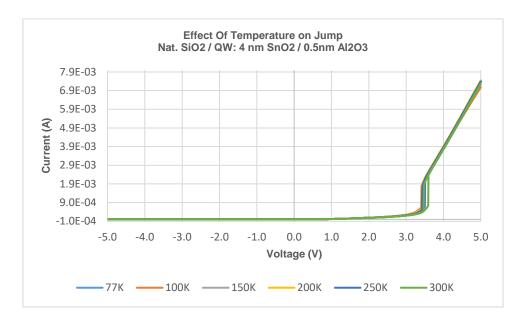

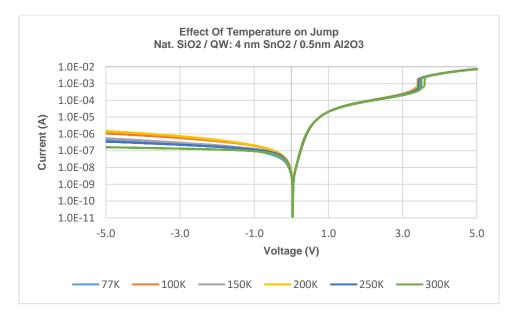

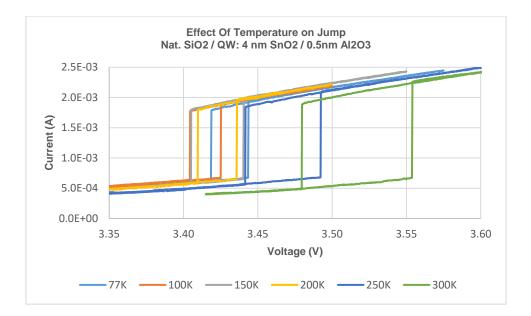

Figure 61: Effect of various low temprature of Source-Silicon IV (Top: In normal scale, Bottom: In Log scale) for device with Native SiO<sub>2</sub> / QW: 4nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

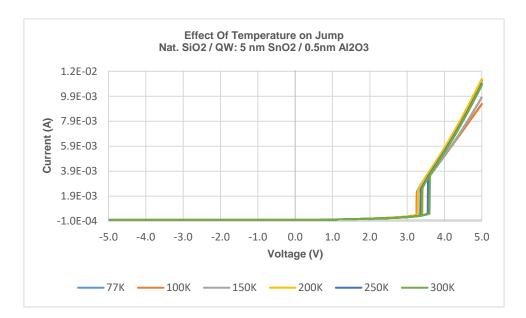

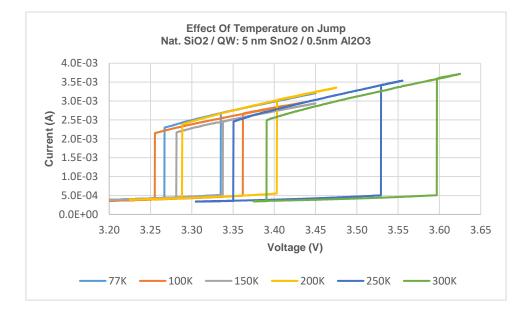

Figure 62: Effect of various low temprature of Source-Silicon IV (Top: In normal scale, Bottom: In Log scale) for device with Native  $SiO_2 / QW$ : 5nm  $SnO_2 / 0.5nm$   $Al_2O_3$ \_RTA 500°C -15min

Figure 63: Effect of various low temprature of Source-Silicon IV with high resolution for device with Native SiO<sub>2</sub> / QW: 3 nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

Figure 64: Effect of various low temprature of Source-Silicon IV with high resolution for device with Native SiO<sub>2</sub> / QW: 4 nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

Figure 65: Effect of various low temprature of Source-Silicon IV with high resolution for device with Native SiO<sub>2</sub> / QW: 5 nm SnO<sub>2</sub> / 0.5nm Al<sub>2</sub>O<sub>3</sub>\_RTA 500°C -15min

### **Chapter 1: Introduction**

The scaling rule allows transistors (MOSFETs) to operate at greater speeds and exponentially larger packing densities<sup>1–4</sup> With the scaling rule, along with many novel MOSFET designs, there have been great enhancements in MOSFET performance over the past few decades. Some examples of these performance enhancers include metal-gate high-k stacks,5-7 channel strain8-10, ultra-thin body designs,11-13 ultra-thinsilicon-on-insulator substrates<sup>14,15</sup> FinFETs<sup>16–19</sup>. body and However, these performance enhancements have recently slowed down. One critical reason is that the voltage scaling <sup>20</sup> cannot be continued due to fundamental thermodynamic limitation. The electron thermal excitation following the Fermi-Dirac distribution imposes a fundamental thermodynamic limitation to the slope of current-voltage (I-V) characteristics (green line in Fig. 1). This prohibits the supply voltage V<sub>dd</sub> from being arbitrarily reduced as lowering V<sub>dd</sub> causes a large amount of Off-state current.

# Figure 1: Subthreshold swing (green) limit at 300K. Blue IV shows desired slope to reduce $V_{dd}$ and Off-state current

The subthreshold slope (SS) is characteristic of the drain current (I<sub>d</sub>) and the gate voltage (V<sub>g</sub>) relationship in a metal-oxide-semiconductor field-effect transistor (MOSFET). SS is defined as the amount of gate voltage change to reduce the current by ten times (unit: mV/decade). This subthreshold slop (SS) is a measure of how sharply transistor can turn on or off in the subthreshold region. The smaller the value of the Subthreshold Slop (SS), the steeper the I-V in the subthreshold region.

For a finite subthreshold slope, the MOSFET needs to maintain High enough  $V_{dd}$  to ensure high enough  $I_{on}$  /  $I_{off}$  ratio. However, as we can see in Figure 1, if we can decrease the subthreshold slope value (stepper slope), we can reduce the  $V_{dd}$  required to maintain a similar current while making  $I_{off}$  small. Therefore, by decreasing the subthreshold slope value (Steeper slope) we can reduce the energy wasted as heat.

The subthreshold slop (SS)<sup>21–23</sup>, is given by,

SS =

$$\frac{dV_{GS}}{d\log(I_D)}$$

= ln(10). $\frac{kT}{q}(1 + \frac{C_d}{C_{ox}})$ \_\_\_\_Eq. (1)

Here V<sub>GS</sub> is the gate-to-source voltage, I<sub>D</sub> is the drain current, C<sub>d</sub> is the depletion-layer capacitance, and C<sub>ox</sub> is the gate-oxide capacitance. We can obtain the theoretical subthreshold if we assume C<sub>d</sub> = 0 and C<sub>ox</sub> =  $\infty$ .

SS =  $\ln(10).\frac{kT}{q}$ \_\_\_\_\_Eq. (2)

From Eq. (1) and Eq. (2), the subthreshold slop (SS) is proportional to the temperature. At room temperature (300K) its theoretical limit is 60 mV/decade.<sup>24</sup> Hence, to reduce the value of the subthreshold slope (steeper slope), it is required that the temperature is lowered. The root cause of the subthreshold slope limit of 60 mV/decade is the Fermi-Dirac electron thermal excitation. Several strategies have been examined to address this undesired thermal excitation of electrons. Tunneling field-effect transistors<sup>25–27</sup> (TFET), which use band-to-band tunneling<sup>28</sup> to reduce Fermi-Dirac thermal excitation<sup>29,30</sup>, are among the most extensively investigated technologies. Here a p-type doped source electrode and n-type doped drain electrode make up most of the TFETs. To reduce the contribution of the Fermi-Dirac thermal excitation, this design uses band-to-band tunneling from the valence band of the p-type source to the conduction band of the n-type drain. Various TFET<sup>31–35</sup> designs with different configurations, such as vertical structures, sidewall gating, planar structures, and nanowires, have been studied. Numerous other material systems, such as lnAs-Si<sup>36–38</sup>, lnAs/GaSb-Si<sup>39–41</sup>, AlGaSb-InAs<sup>42–44</sup>, and 2D semiconductors, have also been explored (e.g., MoTe<sup>245,46</sup>, WSe<sup>247,48</sup>, and MoS<sup>49,50</sup>). Several types of TFET heterostructures have also been investigated.

This study investigates a new energy-filtering architecture that enables cold electron injection to silicon at room temperature with an effective electron temperature of 0.08 Kelvin. This is done by filtering out thermally excited electrons using a quantum well discrete energy level, allowing only the thermally suppressed cold electrons to tunnel into the silicon upon the application of a voltage bias. This architecture effectively suppresses the thermal excitation of electrons when the Si conduction band edge is aligned with the Quantum well (QW) discrete energy level, enabling cold-electron injection to Si at room temperature.

### **Chapter 2: Energy Filtering Principle**

#### 2.1 Concept

It has been demonstrated that thermally excited electrons can be suppressed without the need for external cooling or cryogenic settings<sup>51</sup>. This was accomplished by filtering high energy electrons using a discrete quantum state; as a result, only cold electrons participate in the electron transport.

Figure 2: Energy filtering and cold-electron transport in double-barrier tunneling junction (DBTJ) structure <sup>51</sup>

In the previous work <sup>51</sup>, as seen in Figure 2, the device architecture consists of source metal, a 2nm Cr<sub>2</sub>O<sub>3</sub> layer which forms a quantum well, tunneling barrier 1, a quantum dot as a channel, tunneling barrier 2 and drain metal. In this structure, the thermally excited electrons from the source metal are filtered by the QW energy level of the quantum-well layer before entering the discrete energy levels of the quantum dot and then into the drain electrode. This cold-electron transport has been verified for the 2D (QW) to 0D (quantum dot) system. It would be important to see if the cold-electron transport can be realized for another dimensional system, for example, for 2D to 3D transport. This work investigates the energy-filtered cold-electron transport from 2D (SnO<sub>2</sub> QW) to 3D (Si). Importantly, the investigation of the silicon system will allow the

devices to be fabricated on a large scale as they can be incorporated into existing MOSFET fabrication technologies.

#### 2.2 Principle of Quantum well as Energy filter

When one or more dimensions of a solid shrink to the nanoscale, the confinement of particles leads to discrete quantum states.<sup>52–54</sup> One example of the quantum confinement is a quantum well<sup>55–61</sup>, in which the particles are constrained in one dimension but are free to travel in the other two. Confinements typically occur in nanoscale dimensions between 1 and 10 nm. At this size, the dimensions are comparable to the de Broglie wavelength<sup>62–66</sup> of to the electron.

Figure 3: Schematic showing unaligned Quantum well and Silicon [100] bands

structure

Figure 4: Schematic showing aligned Quantum well and Silicon [100] bands structure

The electron tunneling from a QW to Si needs to satisfy two criteria: 1) energy-Conservation<sup>67–69</sup>, and 2) in-plane momentum Conservation.<sup>70–72</sup> The cold-electron injection can be understood from the E-k diagrams in Figures 3 and 4. When a QW state of SnO<sub>2</sub> is below the conduction band edge of Si (E<sub>C</sub>, s<sub>i</sub>), Figure. 3, there is no configuration that satisfies both energy conservation and in-plane momentum conservation. Accordingly, no electron would tunnel from the QW to Si. When the QW state of SnO<sub>2</sub> is aligned with the conduction band edge of Si (E<sub>C</sub>, s<sub>i</sub>), there is a tunneling path that satisfies both energy conservation and in-plane momentum conservation, Figure. 4. Here, the electrons at the bottom of the QW sub-level (E<sub>SnO2</sub>) can tunnel to the Si conduction band edge (E<sub>C</sub>, s<sub>i</sub>), satisfying both conditions. Since the electrons can only tunnel to the Si conduction band edge from the bottom of the QW sub-level (E<sub>SnO2</sub>), electrons present in the excited state in the source metal will not be able to tunnel into the silicon conduction band. This results in only the thermally suppressed electrons trapped in the QW sub-level to be able to tunnel through when the QW sub-level aligns with the Silicon conduction band. Thus, we observe an abrupt current jump in I-V measurements.

#### **Chapter 3: Fabrication Procedure**

#### 3.1 Chapter fabrication for QW-Si Device

This chapter describes the fabrication process for a quantum-well-mediated silicon electron transport device. In this chapter, we discuss the problems we faced during the manufacturing of the devices and the steps taken to resolve them, such as moisture accumulation on the source pad owing to the Peltier effect<sup>73–75</sup> and the doping residue on the silicon wafer after doping. Floridization of resist. The devices were fabricated on 4-inch silicon wafers with four different doping concentrations: P-Si, P++Si, N-Si, and N++Si. The wafer was processed using various deposition techniques, thermal growth processes, dry and wet etching processes, and multiple photolithography processes. The entire process was carried out in a class-10/100 cleanroom facility at the Nanofab Research Facility at the University of Texas, Arlington.

#### 3.2 Substrate preparation

Bare test-grade four-inch silicon wafers were cleaned of all organic impurities using a piranha solution. Precaution needs to be taken when utilizing acids by wearing complete PPE equipment when handling acids. The Piranha solution was prepared using H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> in a ratio of 3:1, So we will take 60mL of sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) was added to a Pyrex glass Piranha beaker and add 20mL of hydrogen peroxide was added to the same beaker very slowly along the sides of a glass beaker. The wafer was submerged in a freshly prepared piranha solution for 30 minutes, thoroughly rinsed in a DI water bath container for 5 minutes and rinsed in running DI water for a few minutes. Again, it was immersed in a second DI water bath for another 5 minutes.

It was then thoroughly rinsed in running DI water for a few minutes and then slowly blow-dried with nitrogen. After removing the organic impurities, as the wafers are stored in contact with air, a thin layer of silicon dioxide (SiO<sub>2</sub>) is formed, and we will need to strip off native silicon dioxide (SiO<sub>2</sub>) removed using HF (10:1). Precaution needs to be taken when utilizing acids by wearing complete PPE equipment when handling acids. To begin the process, we removed HF at a 10:1 ratio in a Teflon container, and the quadrant was submerged in the container for 5 minutes to allow sufficient time for HF to react with native silicon dioxide (SiO<sub>2</sub>). It was then rinsed in a DI water bath for 5 minutes, followed by rinsing under running DI water for a few minutes. Again, it was immersed in a second DI water bath for another 5 minutes. It was then thoroughly rinsed in running DI water for a few minutes and then slowly blowdried with nitrogen.

#### 3.3 Thermal Oxide Growth

Once the substrates are thoroughly cleaned, the process of growing oxides on bare Si wafers can be started. To grow the wafers, the cleaned wafers were loaded into a quartz boat. Once the wafers are loaded into the boat, they can be loaded into a thermal oxidation chamber (Tystar Oxidation Furnace) to grow a nominal thickness of 250 nm silicon dioxide for the [100] wafer and 450 nm silicon dioxide for the [111] wafer.

Figure 5: Tystar Oxidation Furnace for Thermal Oxidation and nitride of Silicon

Thermal oxides were grown using the dry oxidation method to ensure high-quality oxide growth. The oxidation parameters for silicon wafers with the [100] orientation are as follows:

#### Tyster Thermal Oxidation Furnace: KOHD250.001

Ideal Temperature: 450°C

Boat Out: 15 Minutes

Boat In: 15 Minutes

Ramp 700°C: 30 Minutes; N<sub>2</sub>: 5000 sccm

Stabilize: 30 Minutes; N<sub>2</sub>: 5000 sccm

Ramp 1100°C: 2 Hrs.; N<sub>2</sub>: 5000 sccm

Hold: 3 Hrs. 30 Minutes; O2: 3000 sccm

Anneal: 30 Minutes; N2: 5000 sccm

#### Ramp down 700°C: 2 Hrs.; N<sub>2</sub>: 5000 sccm

#### Hold: 700°C; Till alarm Acknowledged

After the oxide was grown, it was measured using Nanospec at the center of all four quadrant regions and the center of the wafer to confirm the film thickness and uniformity. The 250 nm thermal oxide was used as the passivation layer and as a protection to prevent over-etching in the silicon window pattern in the first mask step.

Thermal oxides were grown using the dry oxidation method to ensure high-quality oxide growth. The oxidation parameters for silicon wafers with [111] orientation are as follows:

#### Tystar Thermal Oxidation Furnace: Dry380nm.001

Ideal Temperature: 450°C

Boat Out: 15 Minutes

Boat In: 15 Minutes

Ramp 700°C: 30 Minutes; N<sub>2</sub>: 5000 sccm

Stabilize: 30 Minutes; N<sub>2</sub>: 5000 sccm

Ramp 1100°C: 1 Hrs.; N<sub>2</sub>: 5000 sccm

Hold: 8 Hrs.; O<sub>2</sub>: 3000 sccm

Anneal: 20 Minutes; N<sub>2</sub>: 5000 sccm

Ramp down at 700°C: 2 Hrs.; N<sub>2</sub>: 5000 sccm

Hold: 700°C; Till alarm Acknowledged

After the oxide was grown, it was measured using Nanospec at the center of all four quadrant regions and the center of the wafer to confirm the film thickness and uniformity. The 450 nm thermal oxide was used as the passivation layer and as a protection to prevent any junk that might accumulate during the dicing of the sample and to prevent over-etching in the silicon window pattern in the first mask step.

#### 3.4 Dicing of Silicon wafers with [111] crystal orientation and cleaning.

After growing a passivation layer on a bare Si wafer, we diced the wafer into 1-inch × 1-inch squares using a DISCO Automatic dicing saw (DAD3220). A dicing machine was used to cut the sample owing to the crystal orientation of the silicon wafer. As expected, a simple scratch may not break the sample in a straight line.

Figure 6: DISCO Automatic dicing saw for dicing the silicon wafers

The dicing equipment uses coolant to keep the blade cool during the dicing operation. Because the coolant contains impurities, it contaminates the silicon wafer. To remove impurities from the top of the silicon dioxide, we used hydrogen fluoride (HF) to etch away the top layer of the silicon dioxide layer until a nominal thickness of approximately 250 nm was left in order to keep the sample conditions the same for all wafers.

#### 3.5 Pattering of Silicon Island Region

After growing a passivation layer on the bare Si wafer, the next step was to pattern the sample with the first mask. In this study, we used photolithography to expose a particular area to react with further etching.

Figure 7: Mask layout showing variation in contact area and gate length

In this process, we created three sample names, A, B, and C, in each quadrant of the silicon wafer, and each sample had four regions, A, B, C, and D. Each region in the sample had seven rows from A to G with variations in the size of the exposed silicon region, and seven columns from 1 to 7 with variations in the distance between the source and drain pads.

#### 3.5.1 Photolithography for silicon window pattern exposure.

Each quadrant was coated with a thin layer of a negative photoresist NR-1000PY of approximately 1 µm using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

500 RPM; 100 RPM/s; 5 Seconds

Step 2:

#### 3000 RPM; 1000RPM/s; 60 Seconds

#### Step3:

#### 0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 seconds on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate<sup>76</sup> Subsequently, the samples were prepared for photolithography pattern exposure.

Figure 8: OAI Aligner Equipment for UV Photolithography

The samples were loaded onto an OIA Aligner for the first mask. As this was the first mask, we aligned the samples to ensure that the quadrant was within the mask area. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode

Pressure setting current: 14 mA

Measured Beam Intensity: 19.6 mW/cm<sup>2</sup>

Exposure Time: 6.1 seconds

Dose: 120 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed

from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the development was completed, the sample was removed and slowly blow-dried with dry nitrogen.

#### 3.5.2 Reactive Ion Etching – Dry Etching

The next step was to expose the Si inside the patterned area. To create a Well structure in the silicon dioxide (SiO<sub>2</sub>) area, we need an anisotropic etch; we start etching with reactive ion etching. To ensure that we do not etch silicon, we leave an 80 nm silicon dioxide (SiO<sub>2</sub>) margin. Ions hitting the silicon during etching can result in a rough silicon surface, which can reduce the device yield by depositing very thin films on the exposed silicon for the energy filter stack. To etch the Silicon dioxide (SiO<sub>2</sub>), we use Technics Macro RIE-8800 equipment.

Figure 9: Technics Macro RIE – 8800 equipment for Reactive Ion Etching

Silicon dioxide (SiO<sub>2</sub>) is etched with a gas mixture of CF<sub>4</sub> and O<sub>2<sup>78–80</sup></sub>; as the equipment does not have endpoint detection, we used the time to calculate the etched SiO<sub>2</sub>. To obtain a stable etch rate, the gas flow, pressure, and power were maintained constant.

During the etching process, there is the possibility of physical sputtering, which can result in impurities accumulating in the window area, resulting in a variation in the etch rate. Therefore, we broke the etching into two parts and cleaned the area with oxygen plasma to remove the impurities and any accumulated photoresist in the window area.

The reactive ion etching parameters were as follows:

Step 1:

Power: 600 W

Pressure: 160 mTorr, CF4: 30 sccm , O2: 3.6 sccm

Time: 136 seconds

Step 2:

Power: 350 W

Pressure: 200 mTorr, O<sub>2</sub>: 11 sccm

Time: 300 seconds

Step 3:

Power: 600 W

Pressure: 160 mTorr, CF4: 30 sccm , O2: 3.6 sccm

Time: 136 seconds

Step 4:

Power: 350 W

Pressure: 200 mTorr, O<sub>2</sub>: 11 sccm

Time: 300 seconds

After the etching process was completed, the photoresist was removed from the sample using acetone and isopropyl alcohol (IPA).

#### 3.5.3 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen. However, even after sonication, some redeposited photoresists remained in the silicon window area.

#### 3.5.4 Sample Cleaning and Measurements

To remove the redeposited photoresist, we used oxygen plasma with Macro RIE-8800 equipment. It was observed that the samples treated for 10 minutes or 20 minutes still had some residue remaining. The 30-minute oxygen clean recipe was able to remove all the residues present in and near the window area.

Figure 10: KLA Tencor-P6 profilometer for profile measurement

The thickness profile of the etched area was measured by using a profilometer (KLA Tencor-P6 profilometer). There should be a discrepancy of approximately 60 nm, which is the same as the thickness measured with the reflectometer, the profile height, and the initial measurement of the silicon dioxide thickness. Next, we proceeded to the next phase of the fabrication process.

#### 3.5.5 Wet Etching and Tunnelling Barrier 2

To remove the remaining silicon dioxide (SiO<sub>2</sub>) and expose the silicon region, we used a wet-etching technique because of the remarkably high selectivity between silicon dioxide (SiO<sub>2</sub>) and silicon (Si) with hydrogen fluoride (HF). In addition to exposing the Si region, we etched slightly more SiO<sub>2</sub> to reduce the overall vertical profile of the device, and ensured that the nominal thickness was approximately 60 nm. The thickness was slightly higher than required because of the limitations of the OIA Aligner. If the thickness is less than 50 nm, the contrast between the etched and unetched regions is challenging to distinguish, resulting in poor alignment during further processing.

To etch the sample using hydrogen fluoride, caution needs to be taken when utilizing acids by wearing complete PPE equipment when handling acids. To begin the process, we removed HF at a 10:1 ratio in a Teflon container, and the sample was submerged in the container for 5 minutes to allow sufficient time for HF to stabilize the etch rate of silicon dioxide (SiO<sub>2</sub>)<sup>81,82</sup>. It was then rinsed in a DI water bath for 5 minutes, followed by rinsing under running DI water for a few minutes. Again, it was immersed in a second DI water bath for another 5 minutes. It was then thoroughly rinsed in running DI water for a few minutes and then slowly blow-dried with nitrogen. To determine the etch rate, the sample is again measured with a reflectometer (Nanometrics Nanospec 4150), and After determining the etch rate, the sample is again placed in the HF Container to remove the remaining silicon dioxide (SiO<sub>2</sub>) till the device's nominal thickness is around 60 nm. The thickness profile of the silicon dioxide sample was measured using a reflectometer (Nanometrics Nanospec 4150), and the profile of the etched area was measured using a profilometer (KLA Tencor-P6 Profilometer). There should be a discrepancy of approximately 60 nm, which is the same as the thickness measured with the reflectometer, the profile height, and the initial measurement of the silicon dioxide thickness. After confirming that the silicon

20

(Si) was exposed, it was left overnight in air to form native silicon dioxide (SiO<sub>2</sub>). This thin layer acts as a tunneling barrier 2.

#### 3.6 Patterning of silicon contact pad.

The silicon window was then covered with native silicon dioxide (SiO<sub>2</sub>). Layer, we can now create a silicon contact for the quantum-well silicon electron-transport device.

The first step was to pattern the silicon contact-pad area using photolithography.

#### 3.6.1 Photolithography for silicon contact-pad pattern exposure.

The same quadrant was coated with a thin layer of negative photoresist NR-1000PY of approximately 1  $\mu$ m, using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

500 RPM; 100 RPM/s; 5 Seconds

Step 2:

3000 RPM; 1000RPM/s; 60 Seconds

Step3:

0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 s on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate Subsequently, the samples were prepared for photolithography pattern exposure.

The samples were loaded onto an OIA aligner for the third mask. We used L marks printed from the first mask to ensure that the gate pad was slightly aligned on the top of the silicon window. After it is aligned, it is slightly shifted upward such that the third mask does not overlap the silicon window. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode Pressure setting current: 14 mA Measured Beam Intensity: 19.6 mW/cm<sup>2</sup> Exposure Time: 6.1 seconds

Dose: 120 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the

development was completed, the sample was removed and slowly blow-dried with dry nitrogen.

#### 3.6.2 Reactive Ion Etching – Dry Etching

The next step was to expose the Si inside the patterned area. To create a contact pad in the silicon dioxide (SiO<sub>2</sub>) area, because the etch rate of silicon dioxide (SiO<sub>2</sub>) to the photoresist is exceedingly high, we start etching with reactive ion etching. To ensure that we do not etch silicon, we leave a 10 nm silicon dioxide (SiO<sub>2</sub>) margin. Ions hitting the silicon during etching can result in a rough silicon surface, which can reduce the device yield by depositing very thin films on the exposed silicon for the energy filter stack. To etch the Silicon dioxide (SiO<sub>2</sub>), we use Technics Macro RIE-8800 equipment

Silicon dioxide (SiO<sub>2</sub>) is etched with a gas mixture of  $CF_4$  and  $O_2$ ; as the equipment does not have endpoint detection, we used the time to calculate the etched SiO<sub>2</sub>. To obtain a stable etch rate, the gas flow, pressure, and power were maintained constant. The reactive ion etching parameters were as follows:

Step 1:

Power: 600 W

Pressure: 160 mTorr, CF4: 30 sccm , O2: 3.6 sccm

Time: 86 seconds

Step 2:

Power: 350 W

#### Pressure: 200 mTorr, O<sub>2</sub>: 11 sccm

#### Time: 60 seconds

After the etching process was completed, the photoresist was removed from the sample using acetone and isopropyl alcohol (IPA).

#### 3.6.3 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen.

#### 3.6.4 Photolithography for overlapping silicon contact pad pattern exposure.

The same quadrant was again coated with a thin layer of negative photoresist NR-1000PY of approximately 1  $\mu$ m using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

#### 500 RPM; 100 RPM/s; 5 Seconds

# Step 2:

## 3000 RPM; 1000RPM/s; 60 Seconds

Step3:

## 0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 s on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate1 Subsequently, the samples were prepared for photolithography pattern exposure.

Figure 11: Ellipsometer for measuring thickness of photoresist

The samples were loaded onto an OIA aligner for the third mask. We used alignment marks printed from the third mask to ensure that the gate pad was aligned on the top of the etched area. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode

#### Pressure setting current: 14 mA

Measured Beam Intensity: 19.6 mW/cm<sup>2</sup>

Exposure Time: 6.1 seconds

Dose: 120 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the development was completed, the sample was removed and slowly blow-dried with dry nitrogen.

#### 3.6.5 Wet Etching of silicon dioxide

To remove the remaining silicon dioxide (SiO<sub>2</sub>) and expose the silicon region, we used a wet-etching technique because of the remarkably high selectivity between silicon dioxide (SiO<sub>2</sub>) and silicon (Si) with hydrogen fluoride (HF).

To etch the sample using hydrogen fluoride, caution needs to be taken when utilizing acids by wearing complete PPE equipment when handling acids. To begin the process, we removed HF at a 10:1 ratio in a Teflon container, and the sample was submerged in the container for 20 seconds to remove the remaining 10 nm of silicon

dioxide (SiO<sub>2</sub>). It was then rinsed in a DI water bath for 5 minutes, followed by rinsing under running DI water for a few minutes. Again, it was immersed in a second DI water bath for another 5 minutes. It was then thoroughly rinsed in running DI water for a few minutes and then slowly blow-dried with nitrogen. Once the silicon was exposed, it was confirmed by measuring the contact current using an I-V probe station and Agilent 4155C. The contact current for 0.01mV should be in the range 0.1 to 0.7  $\mu$ A range. If the current was not within this range, we repeated lift-off, photolithography, and HF etching. Once we confirm the current, we can move to metal deposition.

## 3.6.6 Silicon Contact Metal Pad Deposition.

To establish a good contact on the silicon pad, we used a few metals depending on the wafer doping concentration because we did not want to create a Schottky contact but an Ohmic contact, so we could clearly observe the voltage drop across the energyfilter stack. Therefore, we used aluminum (AI) for all p-type wafers. Nickel (Ni) for ntype wafers. The metals were deposited using two different techniques.

- a. E-beam deposition: For this technique, we used two types of equipment: nickel(Ni) and aluminum (Al).

- 1. AJA E-Beam Deposition

- 2. CHA Solution E-Beam Deposition

In this technique, we loaded our samples into a very high vacuum and used an ebeam to heat them. Evaporated material was deposited on the sample; therefore, the deposition was not conformal. We used this technique to reduce plasmainduced defects<sup>83,84</sup> and gases in the deposition layer; however, it induces defects due to X-ray radiation<sup>85,86</sup> in a semiconductor material. The main limitation of this method is that the material must have low vapor pressure<sup>87</sup>.

In E-beam deposition, we load our samples in the equipment and start the pumpdown process with the help of mechanical pumps and Cryogenic pumps to achieve a very high vacuum in the range of 10<sup>-6</sup> mTorr Range

Figure 12: AJA e-beam evaporator equipment for metal deposition

- b. Sputter Deposition: For this technique, we used two different types of equipment that are mainly used for aluminum deposition.

- 1. AJA Sputter Deposition

- 2. Homebuilt Sputter Deposition

In this technique, we loaded our sample into a very high vacuum and used high-energy ions to knock out the material from the source deposited on the sample. To generate high-energy ions, we used the plasma of an inert gas, argon (Ar), to prevent the gas from interacting with the source ions. The deposition of the material is conformal. The benefits of using sputtering over an e-beam are a better range of materials and control over the stoichiometry of a multi-component system<sup>88,89</sup>. In addition, there was less radiation damage than with e-beam evaporation.

Figure 13: Homebuilt Sputter deposition equipment for DC and RF Sputter deposition

# 3.6.7 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. As the layer of resist is dissolved, it also removes the material deposited on top of the resist, but the material that is still deposited on the silicon will still adder to the silicon pad. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen. Therefore, we are now left with metal pads on the silicon.

## 3.6.8 RTA treatment to establish Ohmic contact

To change the Schottky nature of the Metal and Silicon contacts, we need to heat the samples to diffuse aluminum (AI) in the p-Si substrate to convert the contact area immediately below the metal pad into a p<sup>++</sup>-Si substrate. As the Fermi energy band decreases<sup>90</sup>, the Schottky contact is converted into an ohmic contact. For the n-Si substrate, we used Nickel (Ni) and heated the samples to form a Nickel Silicide (NiSi) at the junction of Nickel (Ni) and Silicon (Si). Because Nickel Silicide (NiSi)<sup>91</sup> has a very low barrier, it acts as an ohmic barrier. By removing the Schottky barrier, we can ensure an exact voltage drop across the energy-filter stack.

To ensure linear contact IV, we experimented with various temperatures and times needed for diffusion for all the various doping levels. We settled on a recipe that would ensure proper ohmic contact IV using an IV probe station and Agilent 4155C Semiconductor Parameter Analyzer.

Figure 14: Si - Si IV showing Ohmic contact for N++Si contact with Ni as contact

metal

For an N++ substrate, we found that 30 Seconds at both 450°C and 500°C showed an ohmic contact, but a 1 minute treatment at different temperatures showed slightly lower resistance as shown in figure 14.

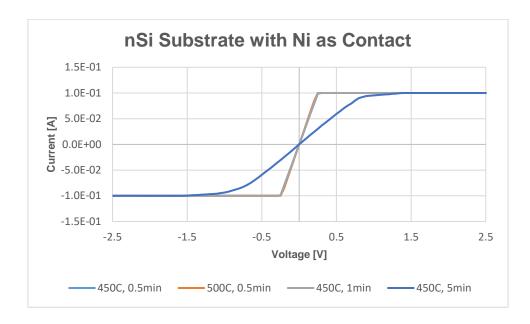

Figure 15: Si - Si IV showing Ohmic contact for n-Si contact with Ni as contact metal

For an N-Si substrate, we found that 30 Seconds at 450°C showed an ohmic contact, but 500°C at 30 Seconds or 1 minute or treatment at different temperatures showed slightly lower resistance as shown in figure 15.

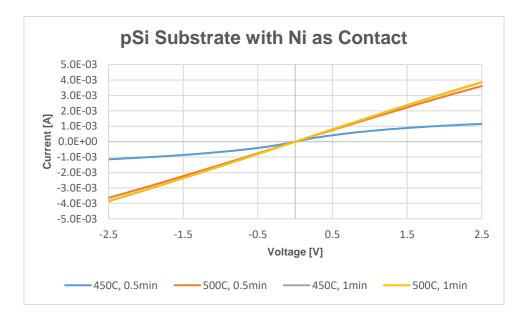

Figure 16: Si - Si IV showing Ohmic contact for p-Si contact with Ni as contact metal

For a P-Si substrate with nickel (Ni), we found that 30 Seconds at 450°C showed an ohmic contact, but at 500°C for 30 Seconds or 1 minute or treatment at different temperatures showed slightly lower resistance as shown in figure 16.

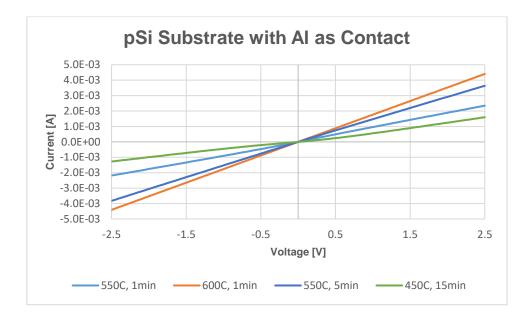

Figure 17: Si - Si IV showing Ohmic contact for p-Si contact with AI as contact metal

For a P-Si substrate with aluminum (AI), we found that 1 min at 550°C or 15 min at 450°C showed an ohmic contact, but 600°C at 1 min lower temperature for a longer treatment time at different temperatures showed a slightly lower resistance as shown in figure 17.

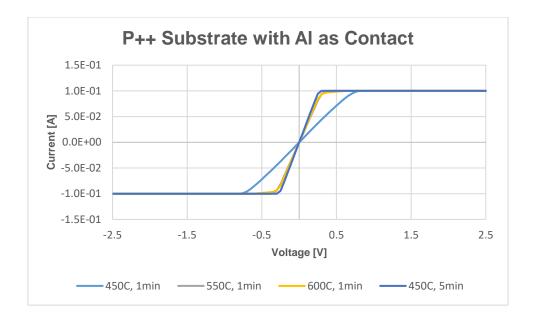

Figure 18: Si - Si IV showing Ohmic contact for P++Si contact with AI as contact

metal

For a P++ substrate with aluminum (AI), we found that 1 min at both 450°C and 500°C showed an ohmic contact, but 600°C at 1 min lower temperature for a longer treatment time at different temperatures showed a slightly lower resistance. as shown in figure 18.

After comparing the different temperatures, to simplify the processing, we chose 500°C for 1 min for nickel (Ni) on N-Si and N++ Si substrates and 600°C for 1 min for aluminum (Al) on p-Si and P++ Si substrates.

Figure 19: JetFirst Rapid Thermal Annealing for Heating samples

# 3.7 Building Energy Filter stack.

The energy filter stack was placed on top of the first mask silicon window in the subsequent phase. There are three layers in the energy filter stack:

Tunnelling Barrier 2: Native Silicon Dioxide

Energy Filter: Quantum Well Layer

Tunnelling Barrier 1: Silicon Nitride or Aluminum Oxide

The first mask window region already has the first layer of the energy filter stack, and after exposing the silicon, we allowed a native silicon dioxide film, which was grown in Section 3.5.5 before the third mask step.

#### 3.7.1 Quantum well layer deposition.

The second layer of the energy-filter stack is a quantum well. We selected varied materials for the formation of the quantum well layers, Cr<sub>2</sub>O<sub>3</sub> and SnO<sub>2</sub>, and found that the tin oxide (SnO<sub>2</sub>) quantum well layers showed the best results. Initially, instead of using tin oxide (SnO<sub>2</sub>), we used to deposit 1.5 nm tin using the e-beam deposition method as the melting temperature of tin (Sn) is low. The CHA E-beam Solution was used. It was then oxidized on a hot plate at 200°C in open air. However, instead of a 1.5 nm tin oxide film, the tin oxide agglomerated and formed a 5 nm spherical ball shape. Therefore, we decided to move towards thin tin oxide (SnO<sub>2</sub>) deposition using the AJA Sputter deposition equipment. The deposition parameters were as follows:

SnO<sub>2</sub> Spark Step 1:

Ignition Pressure: 35 mTorr

Power: 40 W

Ar: 30 sccm

Temperature: Room Temperature

Coat Time: 2 seconds (Plasma ignition)

SnO<sub>2</sub> Spark Step 2:

Ignition Pressure: 35 mTorr

Power: 40 W

Ar: 15 sccm; O<sub>2</sub>: 6sccm

Temperature: Room Temperature

Coat Time: 2 seconds (Plasma ignition)

SnO<sub>2</sub> Deposition

Power: 40 W

Deposition Pressure: 5 mTorr

Ar: 15 sccm; O<sub>2</sub>: 6 sccm

Temperature: Room Temperature

Pre-sputter Time: 120 seconds (required for target cleaning) (Sample shutter is closed.)

Deposition Time: 217.39 s (3nm), 289.85 s (4nm), 362.31 s (5nm)

To determine the deposition rate, we performed deposition on a dummy sample for 600 seconds, and the deposited thickness was measured using an Ocean Optics Reflectometer. The measured thickness was to be 8.28 nm with a 98% fit. The deposition rate is 0.0138 nm/s. This deposition rate was used to deposit different tin oxide thicknesses from 1 nm, 2 nm, 3 nm, 4 nm, 5 nm, 7 nm, and 9 nm for different samples to study the variation within the quantum well thickness and energy level.

Figure 20: Ocean Optics Reflectometer for thickness measurement

# 3.7.2 Tunneling Barrier 1 deposition.

Once the quantum well layer deposition is completed, we will proceed to deposit Tunneling Barrier layer 1. We used silicon nitride (Si<sub>3</sub>N<sub>4</sub>) or aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) as tunneling Barrier 1 material. The silicon nitride tunneling barrier was deposited using AJA Sputter deposition equipment with the following parameters:

Si<sub>3</sub>N<sub>4</sub> Spark Step 1:

Ignition Pressure: 35 mTorr

Power: 40 W

Ar: 15 sccm; N<sub>2</sub>: 6sccm

Temperature: Room Temperature

Coat Time: 2 seconds (Plasma ignition)

Si<sub>3</sub>N<sub>4</sub> Deposition

Power: 150 W

Deposition Pressure: 5 mTorr

Ar: 15 sccm;

To determine the deposition rate, we performed a deposition on a dummy sample, and the deposited thickness was measured using a P-6 Profilometer. A deposition rate of 0.0159 nm/s is obtained for the dummy sample.

For aluminum oxide tunneling barrier, the samples were shipped to Northwestern University to Tyler Gish from Dr Hersam's group using Atomic Layer deposition<sup>92–95</sup> equipment.

The thickness deposited was 0.5 nm and 1.0 nm of aluminum oxide or silicon nitride for different samples with similar thicknesses in the quantum well layer. The thickness of the tunnelling barrier was varied to study the effect of the tunnelling barrier thickness on the shift in the voltage distribution across the energy filter stack and to gain control over the voltage at which we observed the jump. Once the energy-filter stack was deposited, we moved to the next stage of patterning the source and drain metal pads.

We also prepared a few samples without any tunnelling barrier 1.

## 3.8 Source and Drain Contact Metal Pad Deposition.

After completing the energy-filter stack, the sample was patterned using a second mask. We can now create source and drain Pads to test these devices. In the Source

and Darin pads, there is a variation in the distance between the Source and Drain pads with increasing distance from row 1 to row 7.

#### 3.8.1 Photolithography for overlapping silicon contact pad pattern exposure.

The same samples were coated with a thin layer of negative photoresist NR-1000PY of approximately 1  $\mu$ m, using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

500 RPM; 100 RPM/s; 5 Seconds

Step 2:

#### 3000 RPM; 1000RPM/s; 60 Seconds

Step3:

0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 s on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate1 Subsequently, the samples were prepared for photolithography pattern exposure.

The samples were then loaded onto an OIA aligner for the second mask. Alignment marks printed from the first mask were used to ensure that the source and drain pads were aligned at the top of the silicon window. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode Pressure setting current: 14 mA Measured Beam Intensity: 19.6 mW/cm<sup>2</sup> Exposure Time: 10.2 seconds Dose: 200 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the development was completed, the sample was removed and slowly blow-dried with dry nitrogen.

#### 3.8.2 Source - Drain Contact Metal Pad Deposition.

To make contact with our energy filter stack, we used can use different metals depending on their work function of the metals as shown in Figure 22. In the current configuration, we use chromium (Cr) metal, as its work function<sup>96,97</sup> is 4.5 eV. Because chromium has a low melting temperature, the e-beam deposition technique can be

used. For this technique, we used two different types of equipment that are mainly used for chromium (Cr) deposition.

- 1. AJA E-Beam Deposition

- 2. CHA Solution E-Beam Deposition

In this technique, we loaded our samples into a very high vacuum and used an e-beam to heat them. Evaporated material was deposited on the sample; therefore, the deposition was not conformal. We used this technique to reduce plasma-induced defects and gases in the deposition layer; however, it induces defects due to X-ray radiation in a semiconductor material. The main limitation of this method is that the material must have low vapor pressure.

Figure 21: CHA E-Beam Solution for metal deposition

In E-beam deposition, we loaded our samples into the equipment and started the pump-down process with the help of mechanical pumps and cryogenic pumps to achieve a very low vacuum in the range of 10<sup>-6</sup> mTorr Range.

|                            | Ag   | AI   | Au   | Cr   | Ni   | Pt   | W    |

|----------------------------|------|------|------|------|------|------|------|

| ф <sub>м</sub> (in vacuum) | 4.3  | 4.25 | 4.8  | 4.5  | 4.5  | 5.3  | 4.6  |

| n-Ge                       | 0.54 | 0.48 | 0.59 |      | 0.49 |      | 0.48 |

| p-Ge                       | 0.5  |      | 0.3  |      |      |      |      |

| n-Si                       | 0.78 | 0.72 | 0.8  | 0.61 | 0.61 | 0.9  | 0.67 |

| p-Si                       | 0.54 | 0.58 | 0.34 | 0.5  | 0.51 |      | 0.45 |

| n-GaAs                     | 0.88 | 0.8  | 0.9  |      |      | 0.84 | 0.8  |

| p-GaAs                     | 0.63 |      | 0.42 |      |      |      |      |

Figure 22: Table of Various Metal work function<sup>98</sup>

## 3.8.3 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. As the layer of resist is dissolved, it also removes the material deposited on top of the resist, but the material that is still deposited on the silicon will still adder to the silicon pad. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen. Therefore, we are now left with metal pads on the silicon.

## 3.9 RTA for making Quantum well Polycrystalline.

Due to the discrete energy level alignment with the silicon conduction band, it was found that annealing the samples at particular temperatures and lengths caused a rapid fast current spike at particular voltages, demonstrating cold-electron transport. In order to prepare the samples for IV measurements, the RTA chamber heated them. In order to investigate the producing changes of the abrupt, sharp jumps with various annealing conditions, the sample was inserted into the RTA Chamber and heated at various temperatures and periods. The samples may now be processed for electrical characterization because they are ready.

The SnO<sub>2</sub> layer is visible in the TEM picture after Sn was deposited using an e-beam, annealed at 200°C for one hour on a hot plate, and then annealed in an RTA at 500°C for 30 minutes following fabrication. The quantum well created by this method results in an uneven layer thickness of around 5 nm SnO<sub>2</sub>, and it also provides very little control over the actual thickness of the quantum well layer.

## 3.10 Passivation Layer Deposition.

The next step is to deposit the passivation layer to shield the electrodes during subsequent processing once the metal has been deposited. With a thickness of 200 nm, silicon dioxide was used as a passivation layer, and it was deposited using AJA Sputter deposition equipment under the following parameters as follows:

SiO<sub>2</sub> Spark Step 1:

Ignition Pressure: 35 mTorr

Power: 40 W

Ar: 15 sccm; O<sub>2</sub>: 6sccm

Temperature: Room Temperature

Coat Time: 2 seconds (Plasma ignition)

SiO<sub>2</sub> Deposition

Power: 150 W

Deposition Pressure: 5 mTorr

Ar: 30 sccm; O<sub>2</sub>: 6sccm

# Temperature: Room Temperature

Pre-sputter Time: 120 seconds (required for target cleaning) (Sample shutter is

closed.)

Deposition Time: 31,348 seconds

The deposition time for 1 nm silicon dioxide was calculated, from the deposition rate of 0.00637 nm/s obtained for a dummy sample deposition, to be 7837 seconds.

# 3.11 Gold Contact Metal Pad Deposition.

The fabrication of the device was completed. The next step was to establish a good contact between the source, drain, and gate pads. We used gold to ensure good contact, and nickel (Ni) as a bonding layer between different metals to ensure good

contact with various metals. Instead of covering the entire pad, we deposited a small circle on the pads.

## 3.11.1 Photolithography for overlapping silicon contact pad pattern exposure.

The same samples were coated with a thin layer of negative photoresist NR-1000PY of approximately 1  $\mu$ m, using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

500 RPM; 100 RPM/s; 5 Seconds

#### Step 2:

#### 3000 RPM; 1000RPM/s; 60 Seconds

Step3:

0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 s on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate1 Subsequently, the samples were prepared for photolithography pattern exposure.

The samples were then loaded onto an OIA aligner for the second mask. Alignment marks printed from the first mask were used to ensure that the source and drain pads were aligned at the top of the silicon window. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode Pressure setting current: 14 mA Measured Beam Intensity: 19.6 mW/cm<sup>2</sup> Exposure Time: 10.2 seconds Dose: 200 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the development was completed, the sample was removed and slowly blow-dried with dry nitrogen.

## 3.11.2 Via holes etching

The electrodes' metal pads in the pattern region must then be exposed. The passivation layer on the rest of the device will safeguard this area while being utilized to probe the device for I-V characteristic measurements. Therefore, it will be necessary

to expose the metal in the pattern region. Reactive ion etching is used in the Technics Macro RIE - 8800 apparatus to remove the silicon dioxide that is present in the design.

By employing the CF<sub>4</sub>/O2 etch recipe and varying the etch time, the silicon dioxide etch time is determined by optimizing the etch rate. Plotting the various etch periods and thicknesses, it is determined that Silicon dioxide has an etch rate of 0.7 nm/s. We don't need to preserve any margin in this method since the selectivity for SiO<sub>2</sub> v/s Metal is quite good. The Reactive Ion Etching Parameters were as follows:

Step 1:

Power: 600 W

Pressure: 160 mTorr, CF4: 30 sccm , O2: 3.6 sccm

Time: 180 seconds

Step 2:

Power: 350 W

Pressure: 200 mTorr, O<sub>2</sub>: 11 sccm

Time: 60 seconds

However, as the samples are processed by small regions. The photoresist also gets etched away in this process and only a vary thin layer of photo resist is present on the samples. We repeat the photolithography step.

#### 3.11.3 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. As the layer of resist is dissolved, it also removes the material deposited on top of the resist, but the material that is still deposited on the silicon will still adder to the silicon pad. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen. Therefore, we are now left with metal pads on the silicon.

## 3.11.4 Photolithography for overlapping silicon contact pad pattern exposure.

The same samples were coated with a thin layer of negative photoresist NR-1000PY of approximately 1  $\mu$ m, using the spin-coating technique. The quadrant was coated with a resist using a dropper to cover approximately 80% of the surface, and then rotated using a Headway Research PWM32 spin coater. The spin coater was initially spun at low rpm to spread the resist across the sample, and then at high speed to ensure a thin, even coat of resist. The spin-coating parameters were as follows:

Step 1:

500 RPM; 100 RPM/s; 5 Seconds

#### Step 2:

#### 3000 RPM; 1000RPM/s; 60 Seconds

#### Step3:

#### 0 RPM; 1000RPM/s; 0.1 Seconds

After spin-coating, the sample was preheated at 150°C for 60 s on a hotplate. This helps to reduce the residual solvent, which helps in adhesion to the substrate1 Subsequently, the samples were prepared for photolithography pattern exposure.

The samples were then loaded onto an OIA aligner for the second mask. Alignment marks printed from the first mask were used to ensure that the source and drain pads were aligned at the top of the silicon window. Once properly aligned, it was firmly pressed against the hard mask and exposed to UV light to print the pattern on the sample. The exposure parameters were as follows:

Mask mode: Vacuum Contact Mode

Pressure setting current: 14 mA

Measured Beam Intensity: 19.6 mW/cm<sup>2</sup>

Exposure Time: 10.2 seconds

Dose: 200 mJ/cm<sup>2</sup>

After exposing the samples, we performed a post-bake on a hot plate at 100°C, which helped smooth the concentration profile of the photoreaction product via diffusion.<sup>77</sup> The development process was initiated after the sample was cooled. For this purpose, we used a developer called RD-6 for 25 seconds. Teflon tweezers were used to shake the samples while developing to ensure that all the unexposed resist was removed from the sample. This was followed by rinsing in a DI water container for 5 minutes with regular stirring to prevent further development. After the first water bath, it was moved to the second DI water bath for 5 minutes with regular stirring. After the

development was completed, the sample was removed and slowly blow-dried with dry nitrogen. After Confirming a good contact with is present on the Etched via holes with the help of IV probe station and Agilent 4155C Semiconductor Parameter analyzer. We start the process for gold pads deposition

## 3.11.5 Gold Contact Metal Pad Deposition.

Establishing a good contract between the source, drain, and gate pads. We used gold to ensure good contact, and nickel (Ni) as a bonding layer<sup>99–101</sup> between different metals to ensure good contact with various metals. Instead of covering the entire pad, we deposited a small circle on the pads.

For this technique, we used two different types of equipment, mainly used for nickel (Ni) and gold (Au) deposition.

- 1. AJA E-Beam Deposition

- 2. CHA Solution E-Beam Deposition

In this technique, we loaded our samples into a very high vacuum and used an ebeam to heat them. Evaporated material was deposited on the sample; therefore, the deposition was not conformal. We used this technique to reduce plasmainduced defects and gases in the deposition layer; however, it induces defects due to X-ray radiation in a semiconductor material. The main limitation of this method is that the material must have low vapor pressure.

Figure 23: AJA Sputter Deposition equipment for DC and RF Sputtering

In E-beam deposition, we loaded our samples into the equipment and started the pump-down process with the help of mechanical pumps and cryogenic pumps to achieve a very low vacuum in the range of 10<sup>-6</sup> mTorr Range.

# 3.11.6 Lift-off of the photoresist.

Because the photoresist was soluble in acetone, it was immersed in an acetone bath and sonicated for 5 minutes to expedite its dissolution. As the layer of resist is dissolved, it also removes the material deposited on top of the resist, but the material that is still deposited on the silicon will still adder to the silicon pad. After sonication, the samples were removed and rinsed quickly with isopropyl alcohol (IPA). IPA rinsing was performed after acetone to ensure that no acetone residue remained if acetone was dried on the sample surface. After rinsing, the solution was placed in isopropyl alcohol (IPA) and sonicated for 5 minutes. After sonication, the sample was removed and blow-dried slowly using dry nitrogen. Therefore, we are now left with metal pads on the silicon.

# Chapter 4: Result and discussion

# 4.1 Electrical Characterization

After completing the device fabrication process, we started with IV measurements using an IV probe station with an Agilent 4155C Semiconductor Parameter analyzer. Three probes were used in the probe-station arrangement inside the cleanroom. The probes were linked to a parameter analyzer using a connection hub. Individual SMU units were attached to the probes and connected to a parameter analyzer.

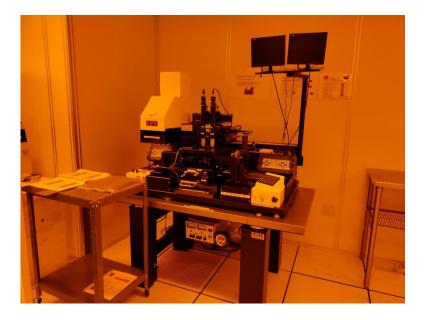

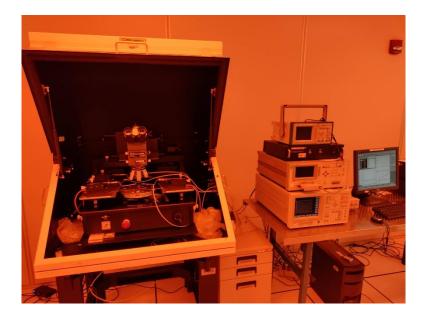

Figure 24: IV Probe station with Agilent 4155C equipment for IV measurement

The majority of the devices were concerned with moisture development during measurement, according to Agilent 4155C current-voltage measurements taken within the cleanroom. As the probe tips come into contact with the source metal surface, moisture begins to develop and spread outward. We believe that the fast heating and cooling of cold electrons as they move from the QW layer to the silicon surface causes moisture to develop owing to the Peltier effect.

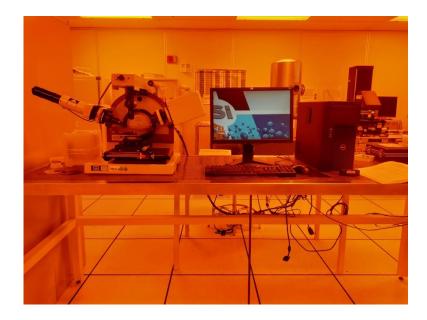

Therefore, further measurements were performed under vacuum using the Agilent ES2708 apparatus and the Janis ST-500 Probe station at the Nanofab lab to prevent the formation of moisture on good devices during the measurement process. IV measurements were performed at low temperatures using a liquid nitrogen tank and a LakeShore 331 temperature controller, which uses a heater to maintain the temperature at the set point and controls the ramp rate of cooling and heating to avoid thermal shock to the sample.

Figure 25: Wiring diagrams of IV measurement equipment