# FABRICATION, CHARACTERIZATION AND HALL MOBILITY ANALYSIS OF MOS DEVICES WITH LOW K AND HIGH K DIELECTRIC MATERIALS

by

## RAKSHIT AGRAWAL

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2006

Copyright © by Rakshit Agrawal 2006

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

I would like to thank Dr. Wiley P. Kirk for giving me a great opportunity to work on this project. His invaluable guidance and motivation has been primarily instrumental in my Master's research over the last one and a half years. He gave me ample freedom to express my views and implement my ideas and encouraged me throughout, which gave me a good insight of some of the most difficult and interesting aspects of semiconductor processing and characterization.

I would like to thank Dr. Zeynep Celik-Butler and Dr. Weidong Zhou for being part of my thesis committee.

I would also like to thank Mr. Robert T. Bate whose insight and guidance have been very important and encouraging towards the completion of my thesis.

I have had an opportunity to work with some very talented colleagues, both past and present. I would like to thank Dr. Kevin Clark and Mr. Eduardo Maldonado who have been a terrific support both inside the UTA NanoFab Center cleanroom where a large part of my project was carried out as well as in the ARS measurements laboratory. Many thanks to other members of my research group Karan Deep, Moshe Davis, Sharukh Chinoy, Rahul Mahajan and Y. Sampathkumar for their support and help. I would also like to thank Vinayak Shamanna and Ram Subramanium for sharing their views and ideas with me. I would like to thank Dr. Nasir Basit and Mr. Dennis Beuno

for their help with the equipment training. I am thankful to all my other colleagues at the NanoFab Center for their help and support at various stages of this project.

Last but not the least, I would like to thank my family Chandita, my sisters Ruchika and Saakshi, and my parents Navin and Vibha for their tremendous support and encouragement over the course of my studies here. I dedicate this thesis to them.

November 22, 2006

#### **ABSTRACT**

FABRICATION, CHARACTERIZATION AND HALL MOBILITY ANALYSIS ON MOS DEVICES WITH LOW K AND HIGH K DIELECTRIC MATERIALS

Publication No.

Rakshit Agrawal, M.S.

The University of Texas at Arlington, 2006

Supervising Professor: Dr. Wiley P. Kirk

Scaling of MOSFETS has led to leakage current problems in SiO<sub>2</sub> dielectric based MOSFETS. This has led to the introduction of high-k dielectric materials which can afford greater physical thickness and achieve the same capacitance with lesser equivalent oxide thickness. But the high-k devices have certain limitations like channel mobility degradation. Mobility degradation in high-k MISFETS is discussed in this work using Hall measurements.

The MOS devices were fabricated with SiO<sub>2</sub> and HfSiO, on p-type silicon substrate. The fabrication process flow used for both type of MOS devices is explained. Characterization and analysis was performed for the determination of various parameters related to these devices like dielectric thickness. Hall mobility

V

measurements were performed on the specially designed multi-drain Hall bars for different gate biases in low magnetic field regime. Higher Hall mobility was observed in the  $SiO_2$  based devices than HfSiO based devices.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                      | iii   |

|-----------------------------------------------------------------------|-------|

| ABSTRACT                                                              | v     |

| LIST OF ILLUSTRATIONS                                                 | X     |

| LIST OF TABLES                                                        | xviii |

| Chapter                                                               | Page  |

| 1. INTRODUCTION                                                       | 1     |

| 1.1 Historical Perspective                                            | 1     |

| 1.2 Theory of MOSFETS                                                 | 5     |

| 1.2.1 Structure of MOSFET.                                            | 6     |

| 1.2.2 The MOS system under External Bias-Operating Modes of a MOSFET  | 8     |

| 1.2.3 Threshold Voltage.                                              | 12    |

| 1.2.4 Gate Oxide                                                      | 14    |

| 1.2.5 Carrier Mobility and Current Density                            | . 15  |

| 1.3 Channel Mobility Degradation Mechanisms in a MOSFET               | 18    |

| 1.3.1 Charge Scattering Mechanisms.                                   | 19    |

| 1.3.2 Charge Trapping Mechanisms                                      | 23    |

| 1.4 High-K Dielectric Materials as an Alternative to SiO <sub>2</sub> | 27    |

| 1.5 Mobility Degradation in High-K Dielectric Materials               | 34    |

|    | 1.6 Methods of Mobility Extraction                             | 37  |

|----|----------------------------------------------------------------|-----|

|    | 1.6.1 The Hall Effect.                                         | 37  |

|    | 1.6.2 Split C-V Measurements                                   | 41  |

| 2. | FABRICATION OF MOS DEVICES.                                    | 44  |

|    | 2.1 Introduction.                                              | 44  |

|    | 2.2 Fabrication of MOS Devices.                                | 50  |

|    | 2.3 Fabricated Devices and Dimensions.                         | 60  |

| 3. | CHARACTERIZATION OF MOS DEVICES.                               | 75  |

|    | 3.1 Introduction.                                              | 75  |

|    | 3.1.1 Current-Voltage (I-V) Characteristics                    | 75  |

|    | 3.1.2 Capacitance-Voltage (C-V) Characteristics                | 78  |

|    | 3.2 Measurement Method and Equipment.                          | 82  |

|    | 3.3 Experimental I-V characteristics                           | 84  |

|    | 3.3.1 Samples with SiO <sub>2</sub> as Gate Dielectric         | 84  |

|    | 3.3.2 Samples with HfSiO as Gate Dielectric                    | 91  |

|    | 3.4 Experimental C-V characteristics.                          | 99  |

|    | 3.4.1 Samples with SiO <sub>2</sub> as Gate Dielectric         | 99  |

|    | 3.4.2 Samples with HfSiO as Gate Dielectric                    | 112 |

| 4. | HALL MOBILITY MEASUREMENTS                                     | 126 |

|    | 4.1 Introduction.                                              | 126 |

|    | 4.2 Packaging.                                                 | 129 |

|    | 4.3 Hall Mobility Measurement Method and Measurement Equipment | 134 |

| 4.4 Hall Mobility Measurements-Experimental Results                   | 138 |

|-----------------------------------------------------------------------|-----|

| 4.4.1 Samples with SiO <sub>2</sub> as Gate Dielectric                | 139 |

| 4.4.2 Samples with HfSiO as Gate Dielectric                           | 161 |

| 4.5 Comparison of Hall Mobility in SiO <sub>2</sub> and HfSiO samples | 168 |

| 5. CONCLUSION.                                                        | 172 |

| 5.1 Summary                                                           | 172 |

| 5.2 Future Work                                                       | 175 |

| APPENDIX                                                              |     |

| A. MASKS FOR FABRICATION                                              | 178 |

| B. FABRICATION RECIPES                                                | 182 |

| REFERENCES                                                            | 195 |

| DIOCDADUICAT INFORMATION                                              | 204 |

# LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                  | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Moore's law of scaling                                                                                                           | 2    |

| 1.2    | Different kinds of MOSFETS                                                                                                       | . 6  |

| 1.3    | Basic structure of an n-channel MOSFET                                                                                           | . 7  |

| 1.4    | Energy band diagram of a MOS system operating in accumulation.                                                                   | 9    |

| 1.5    | a) Energy band diagram of a MOS system operating in depletion     b) Cross-sectional view of a MOS system operating in depletion | . 10 |

| 1.6    | a) Energy band diagram of a MOS system operating in inversion     b) Cross-sectional view of a MOS system operating in inversion | . 11 |

| 1.7    | Random motion of carriers in a semiconductor with and without applied electric field                                             | . 16 |

| 1.8    | Electron and hole mobility versus doping density for silicon                                                                     | . 21 |

| 1.9    | Temperature dependence of the surface roughness limited mobility                                                                 | . 23 |

| 1.10   | Fixed charge effects on the capacitance-voltage curve of a MOS system                                                            | . 24 |

| 1.11   | Four categories of oxide charges in a MOS system                                                                                 | . 24 |

| 1.12   | High-k for gate dielectrics                                                                                                      | . 29 |

| 1.13   | Conduction band and valence band offsets of various oxides on Silicon                                                            | . 31 |

| 1.14   | Defect formation at the poly-Si and high-k dielectric interface                                                                  | 33   |

| 1.15   | Reduction in maximum mobility with decreasing thickness of interfacial oxide.                                                    | . 35 |

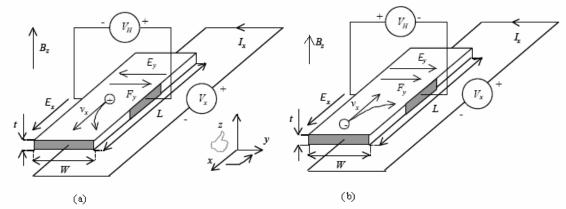

| 1.16 | Hall setup and carrier motion for a) holes b) electrons                                           | 37 |

|------|---------------------------------------------------------------------------------------------------|----|

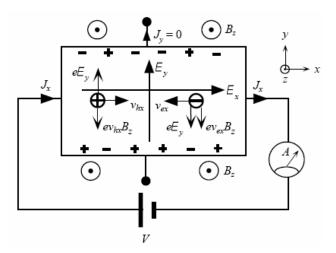

| 1.17 | Hall Effect for ambipolar conduction in a semiconductor with both electrons and holes             | 38 |

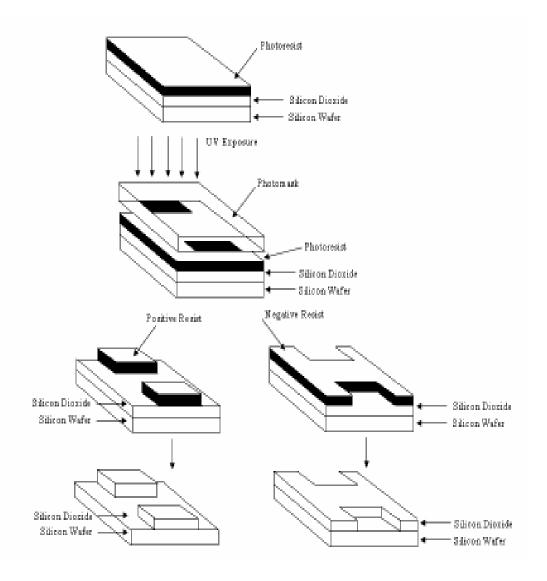

| 2.1  | Exposure and development of negative and positive photoresists and resulting etched film patterns | 45 |

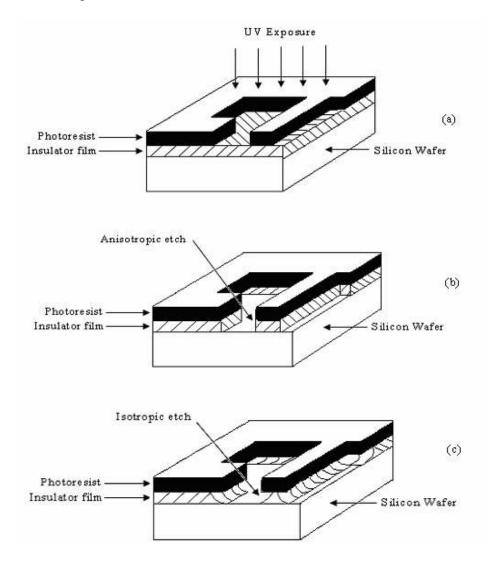

| 2.2  | Comparison between (b) isotropic etch and (c) anisotropic etch                                    | 48 |

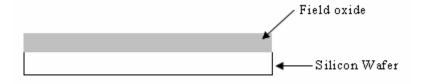

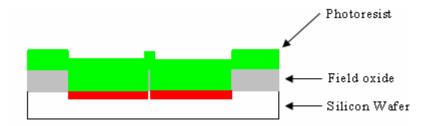

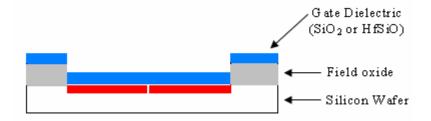

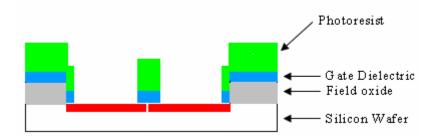

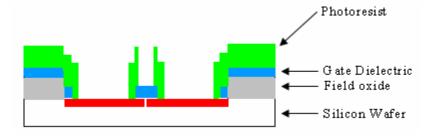

| 2.3  | Field Oxidation of silicon wafer                                                                  | 50 |

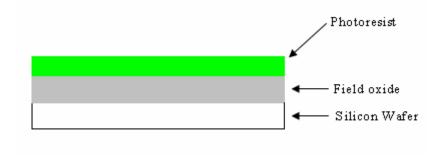

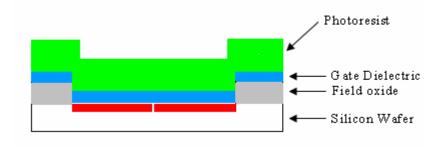

| 2.4  | Spinning of Photoresist AZ 2020.                                                                  | 51 |

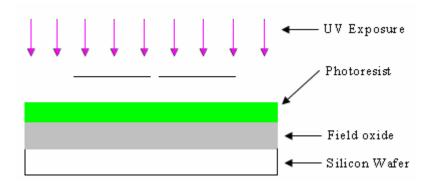

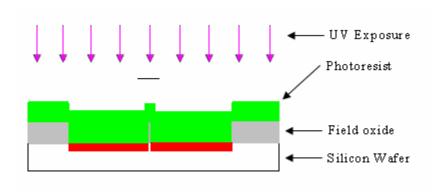

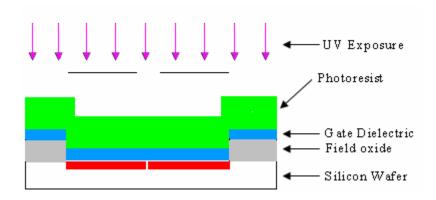

| 2.5  | Exposure using UV light                                                                           | 51 |

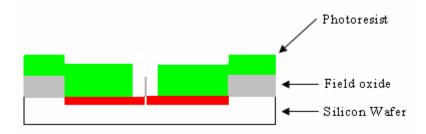

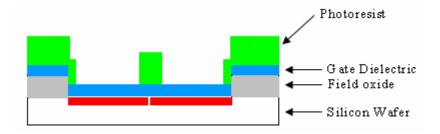

| 2.6  | Develop using AZ 300MIF developer.                                                                | 52 |

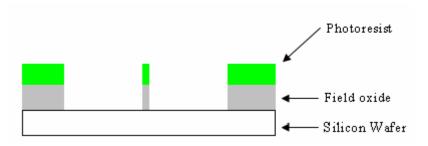

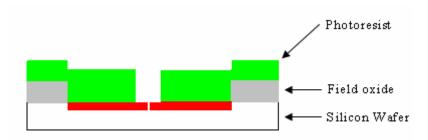

| 2.7  | Field oxide etch.                                                                                 | 52 |

| 2.8  | Photoresist removal using AZ 400T                                                                 | 52 |

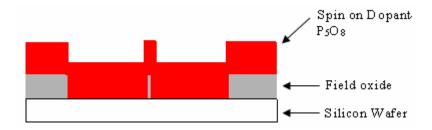

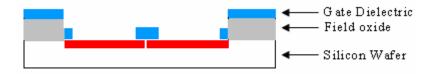

| 2.9  | SOD coating and anneal                                                                            | 53 |

| 2.10 | Drive-in diffusion                                                                                | 53 |

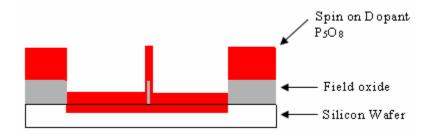

| 2.11 | Post diffusion clean                                                                              | 53 |

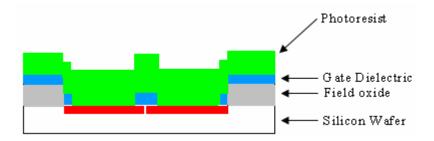

| 2.12 | Spinning of Photoresist AZ 2020                                                                   | 54 |

| 2.13 | Exposure using UV light                                                                           | 54 |

| 2.14 | Develop using AZ 300MIF developer                                                                 | 55 |

| 2.15 | Channel Oxide etch.                                                                               | 55 |

| 2.16 | Photoresist removal using AZ 400T                                                                 | 55 |

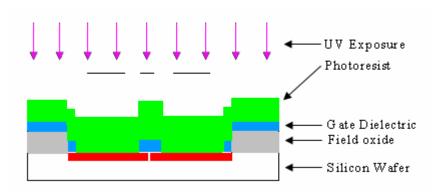

| 2.17 | Growth or deposition of gate dielectric                                                           | 56 |

| 2.18 | Spin-coating of Photoresist AZ 2020                                                               | 56 |

| 2.19 | Exposure using UV light                                                                           | 57 |

| 2.20 | Develop using AZ 300MIF                            | . 57 |

|------|----------------------------------------------------|------|

| 2.21 | Gate dielectric etch                               | . 58 |

| 2.22 | Removal of photoresist using AZ 400T               | . 58 |

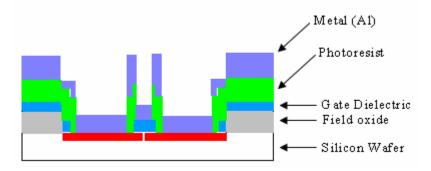

| 2.23 | Spin-coating of Photoresist AZ 2020                | . 58 |

| 2.24 | Exposure using UV light                            | . 59 |

| 2.25 | Develop using AZ 300MIF.                           | . 59 |

| 2.26 | Metal (Al) deposition using thermal evaporation    | . 60 |

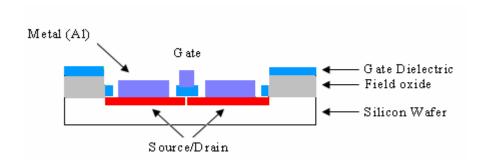

| 2.27 | Metal lift off by AZ 400T                          | . 60 |

| 2.28 | L-Edit layout of MOSFETS with different W/L ratios | . 61 |

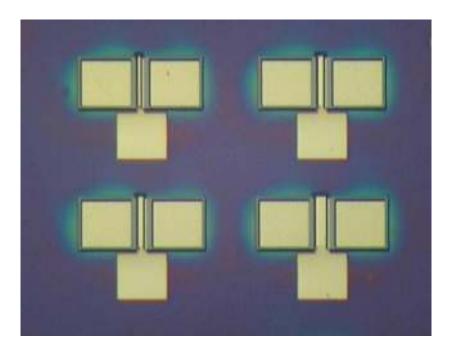

| 2.29 | MOSFETS after fabrication.                         | . 62 |

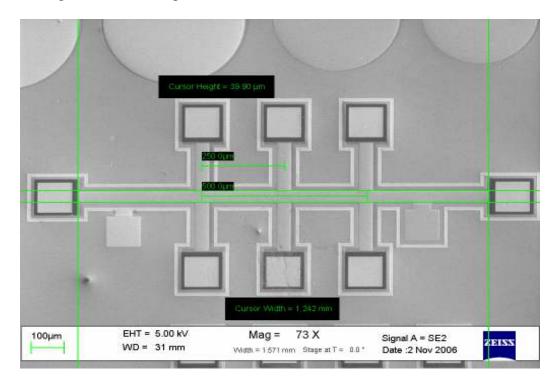

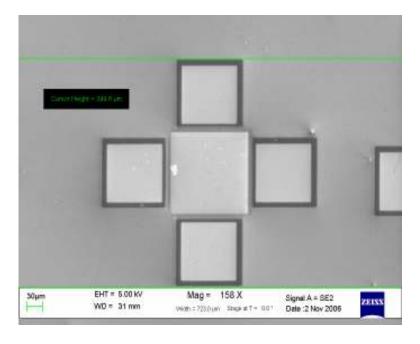

| 2.30 | SEM image of the fabricated MOSFETS                | . 62 |

| 2.31 | L-Edit layout of MOS Capacitors                    | . 63 |

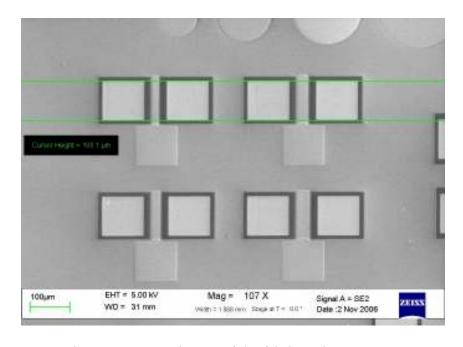

| 2.32 | MOS Capacitors after fabrication                   | .63  |

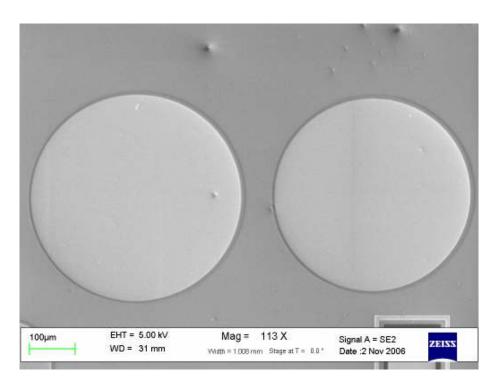

| 2.33 | SEM images of fabricated MOS Capacitors            | . 64 |

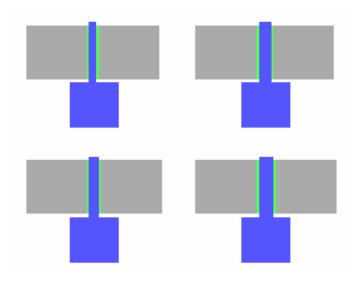

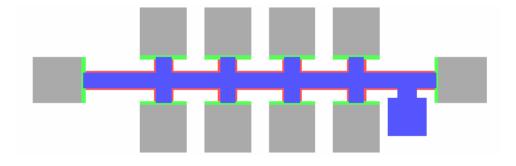

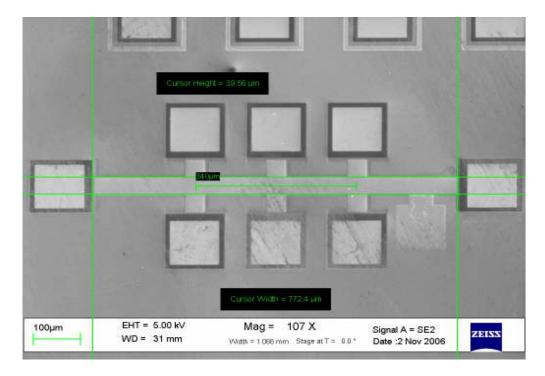

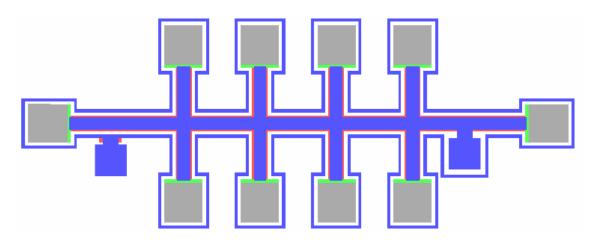

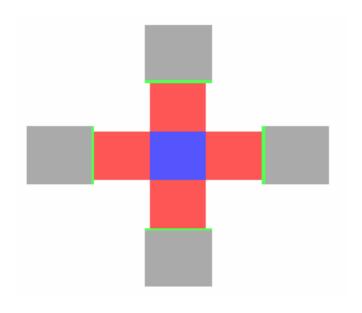

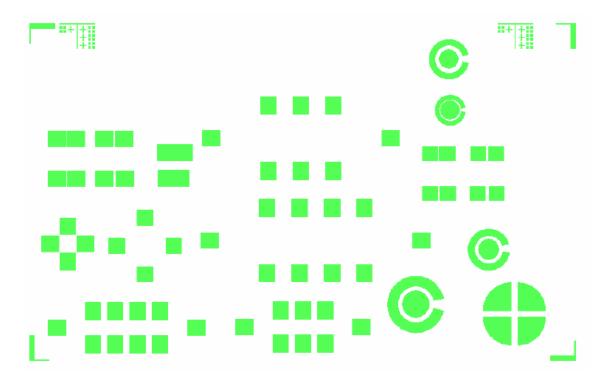

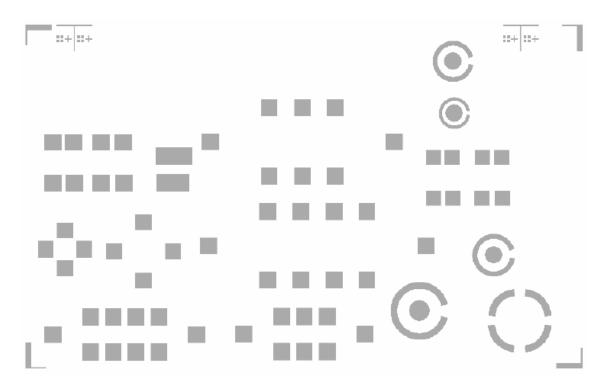

| 2.34 | L-Edit layout of Hall-Bar1                         | . 64 |

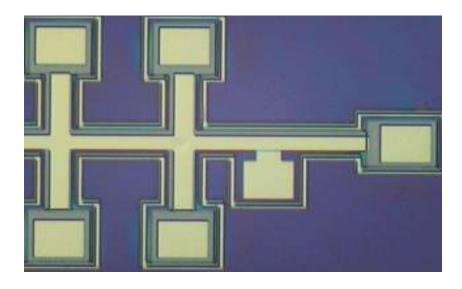

| 2.35 | SEM image of fabricated Hall-Bar1                  | . 65 |

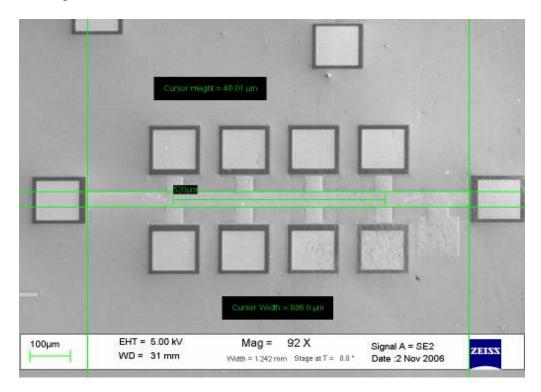

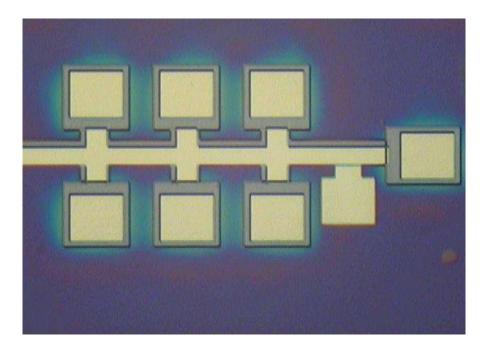

| 2.36 | L-Edit layout of Hall-Bar 2.                       | 65   |

| 2.37 | SEM image of fabricated Hall-Bar 2.                | . 66 |

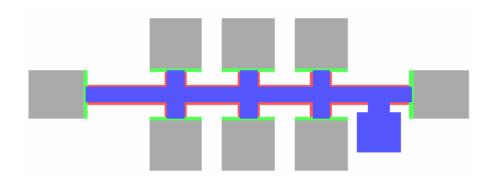

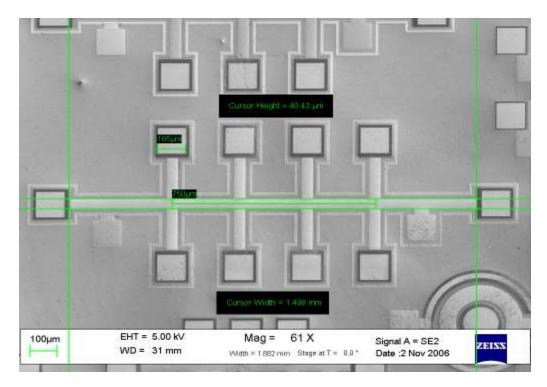

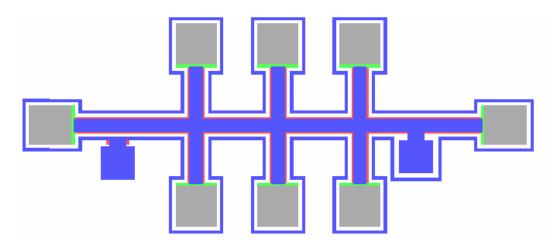

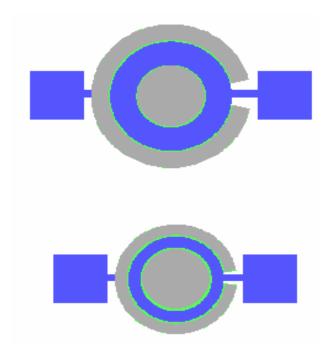

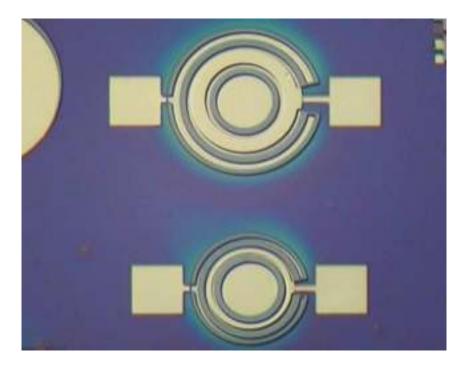

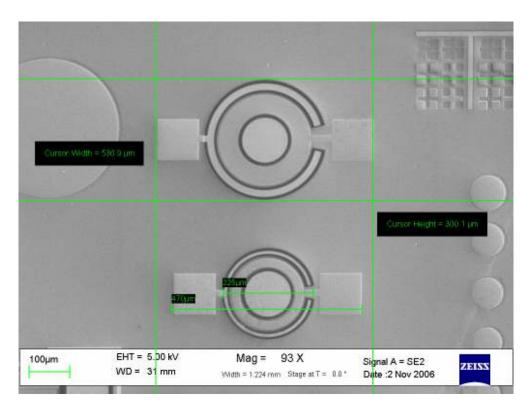

| 2.38 | L-Edit layout of Hall-Bar-ring 1                   | . 66 |

| 2.39 | SEM image of fabricated Hall-Bar ring 1            | 67   |

| 2.40 | L-Edit layout of Hall-Bar ring 2                   | 67   |

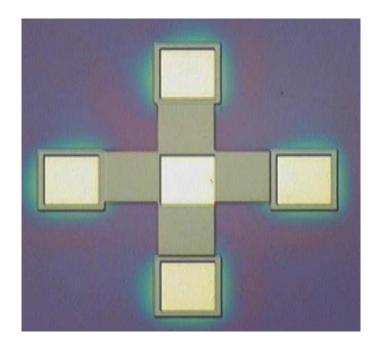

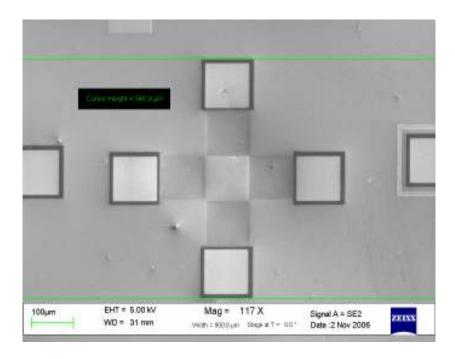

| 2.41 | SEM image of fabricated Hall-Bar ring 2                                        | 68 |

|------|--------------------------------------------------------------------------------|----|

| 2.42 | Hall-Bar ring 2 after fabrication                                              | 68 |

| 2.43 | Hall-Bar 2 after fabrication                                                   | 69 |

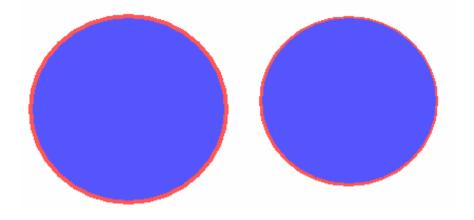

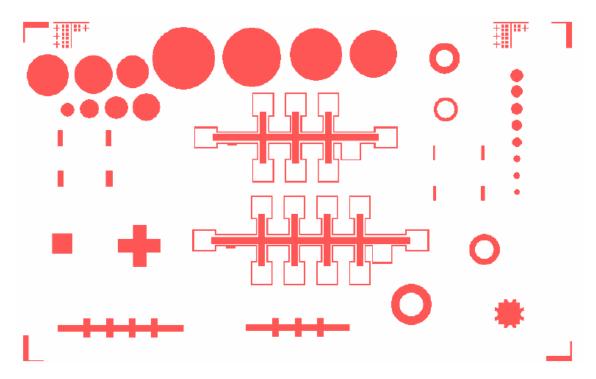

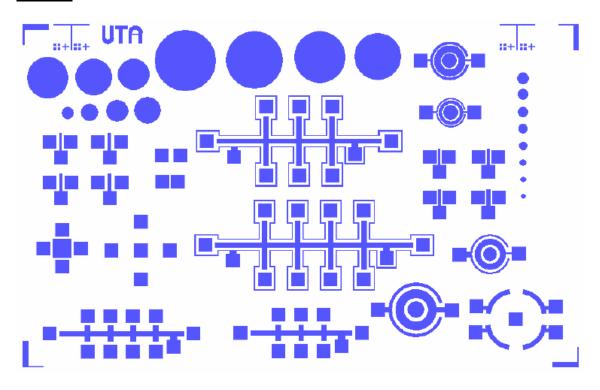

| 2.44 | L-Edit layout of Carbino discs                                                 | 70 |

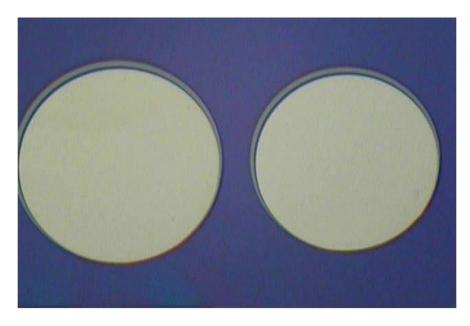

| 2.45 | Carbino discs after fabrication.                                               | 70 |

| 2.46 | SEM image of fabricated Carbino discs.                                         | 71 |

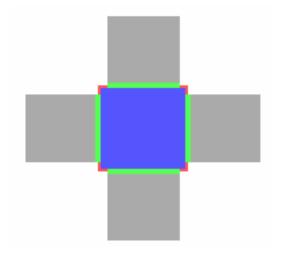

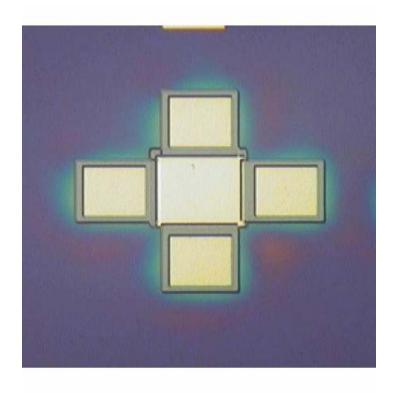

| 2.47 | L-Edit layout of Van Der Pauw device 1.                                        | 71 |

| 2.48 | Van Der Pauw device 1 after fabrication                                        | 72 |

| 2.49 | SEM image of fabricated Van Der Pauw device 1                                  | 72 |

| 2.50 | L-Edit layout of Van Der Pauw device 2                                         | 73 |

| 2.51 | Van Der Pauw device 2 after fabrication                                        | 73 |

| 2.52 | SEM image of fabricated Van Der Pauw device 2                                  | 74 |

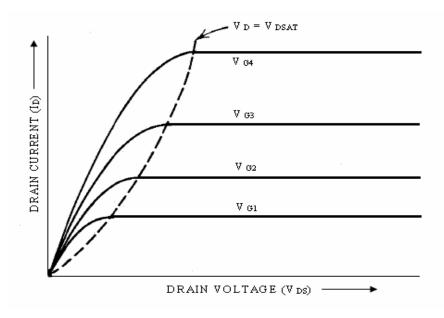

| 3.1  | Ideal I <sub>d</sub> Vs V <sub>ds</sub> characteristics for n-channel MOSFET   | 76 |

| 3.2  | General behavior of C-V curves of an ideal MOS system                          | 81 |

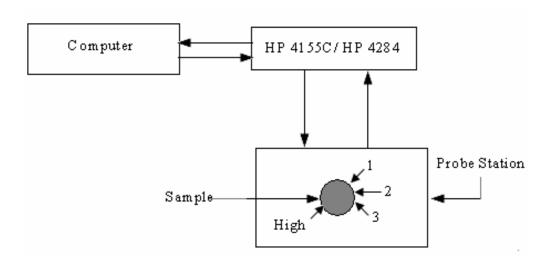

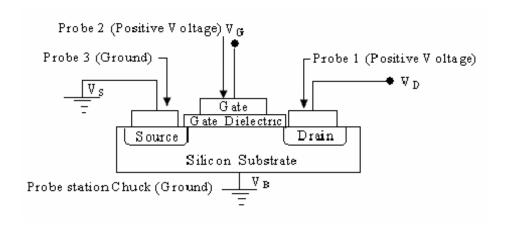

| 3.3  | Probe-station and the parameter analyzers controlled by computer               | 82 |

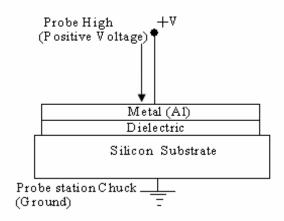

| 3.4  | $I_d \ Vs \ V_{ds}$ measurement setup                                          | 83 |

| 3.5  | C-V measurement setup                                                          | 84 |

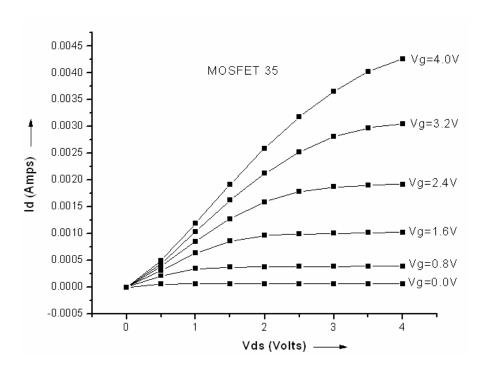

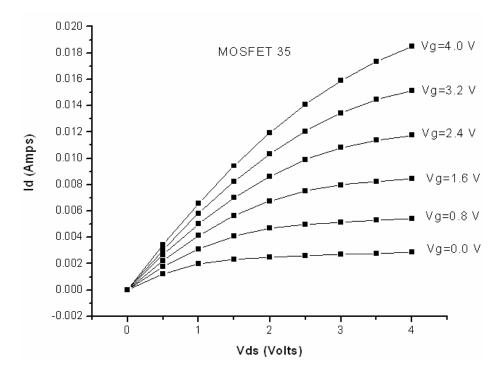

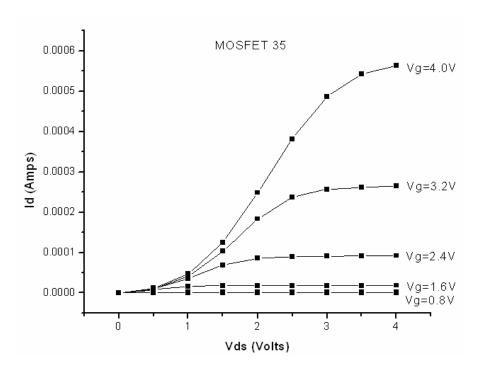

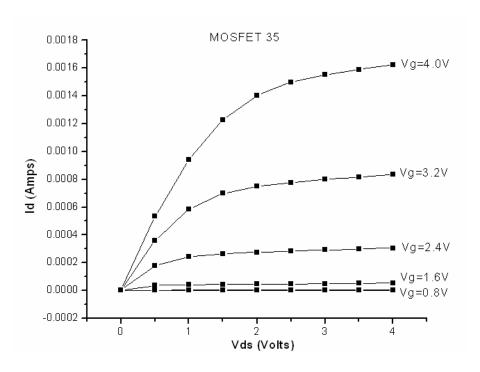

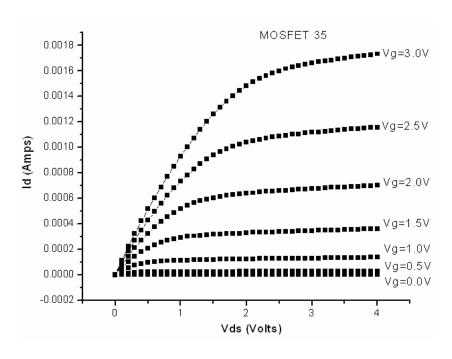

| 3.6  | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample SI 001  | 85 |

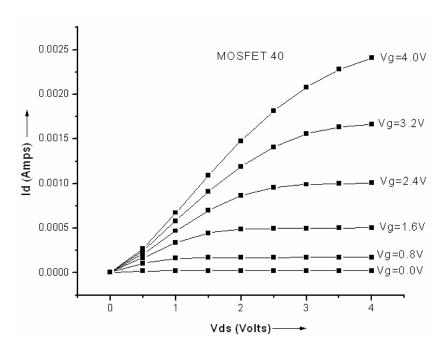

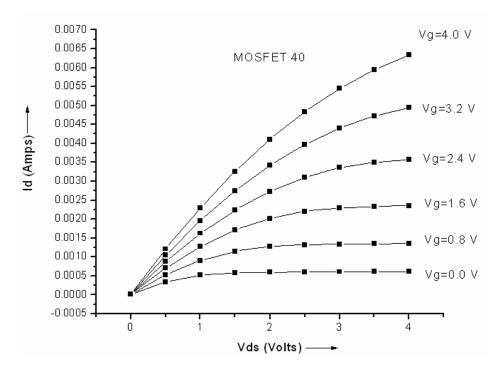

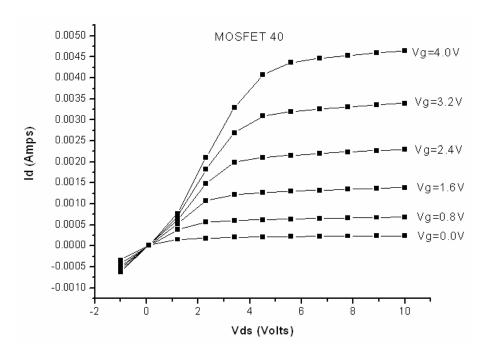

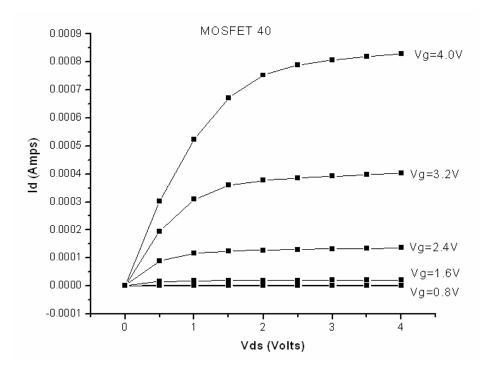

| 3.7  | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample SI 001  | 85 |

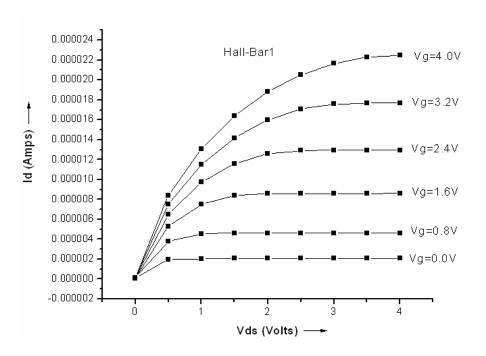

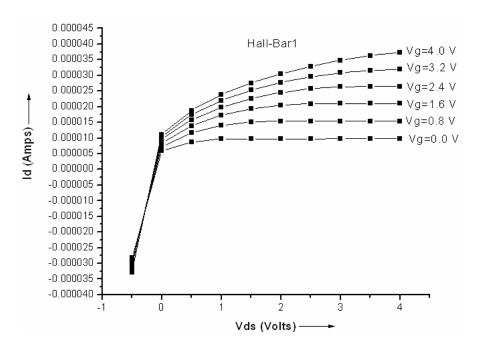

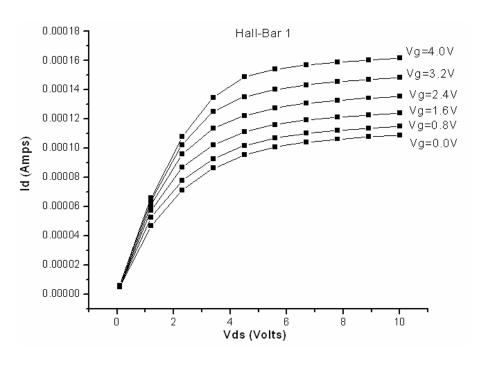

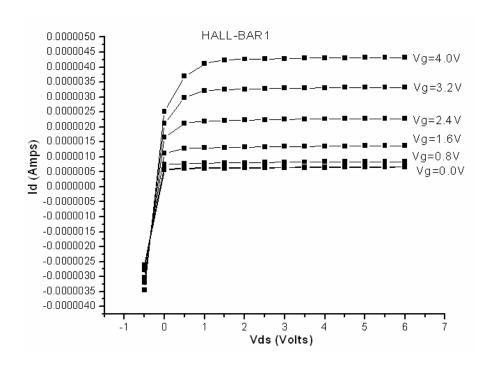

| 3.8  | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 1, sample SI 001 | 86 |

| 3.9  | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample SI 002  | 87 |

| 3.10 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample SI 002  | 87 |

| 3.11 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 1, sample SI 002                   |

|------|--------------------------------------------------------------------------------------------------|

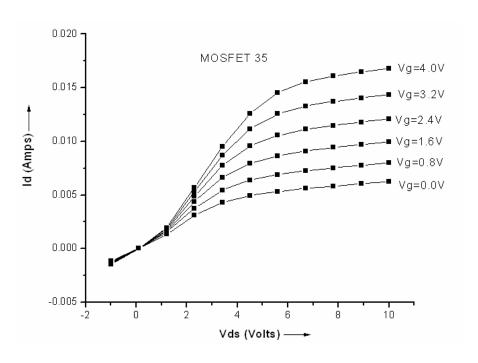

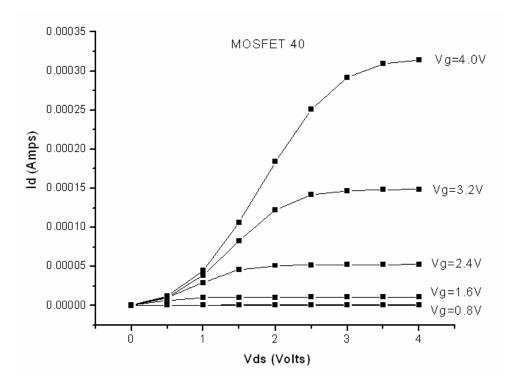

| 3.12 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample SI 003                    |

| 3.13 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample SI 003                    |

| 3.14 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 1, sample SI 003                   |

| 3.15 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample HK 008                    |

| 3.16 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample HK 008                    |

| 3.17 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 1, sample HK 008                   |

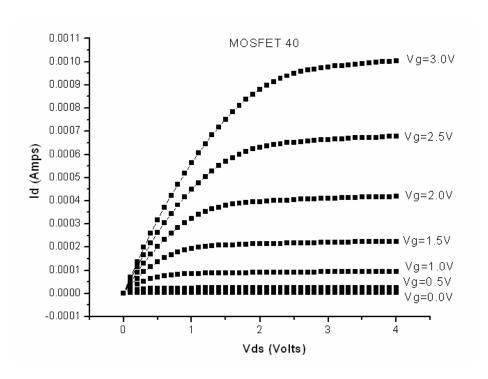

| 3.18 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample HK 009                    |

| 3.19 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample HK 009                    |

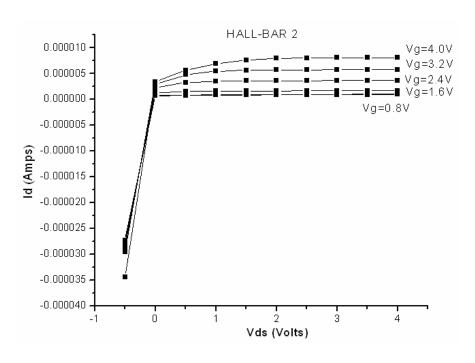

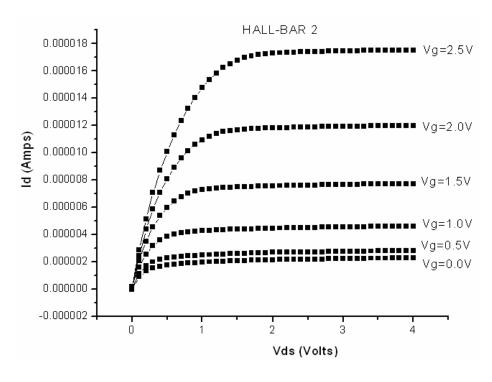

| 3.20 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 2, sample HK 009                   |

| 3.21 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 35, sample HK 010                    |

| 3.22 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of MOSFET 40, sample HK 010                    |

| 3.23 | I <sub>d</sub> Vs V <sub>ds</sub> characteristics of Hall-Bar 2, sample HK 010                   |

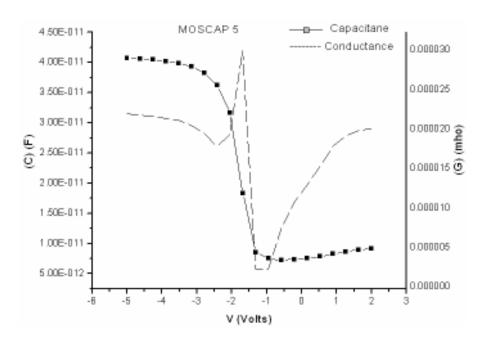

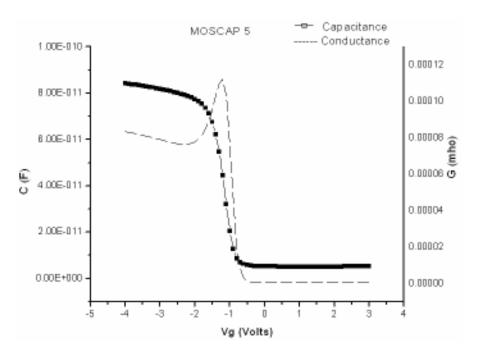

| 3.24 | C-V characteristics of MOSCAP 5, sample SI 001                                                   |

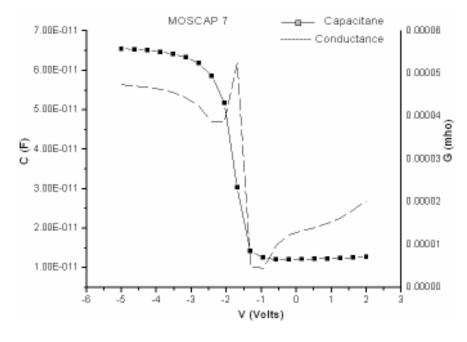

| 3.25 | C-V characteristics of MOSCAP 7, sample SI 001100                                                |

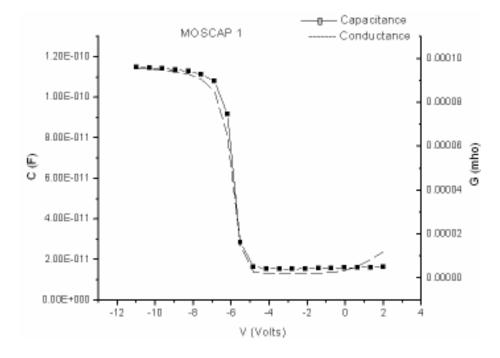

| 3.26 | C-V characteristics of MOSCAP 1, sample SI 002                                                   |

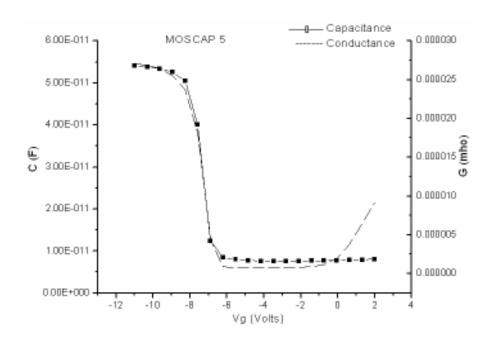

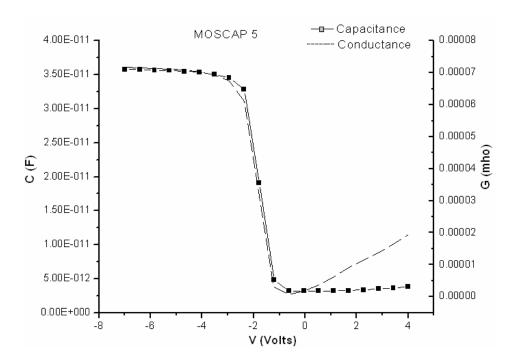

| 3.27 | C-V characteristics of MOSCAP 5, sample SI 002                                                   |

| 3.28 | C-V characteristics of MOSCAP 5, sample SI 003                                                   |

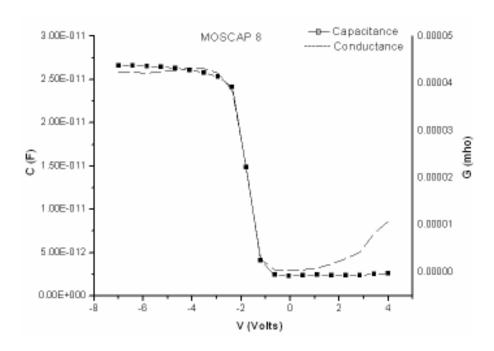

| 3.29 | C-V characteristics of MOSCAP 8, sample SI 003                                                   |

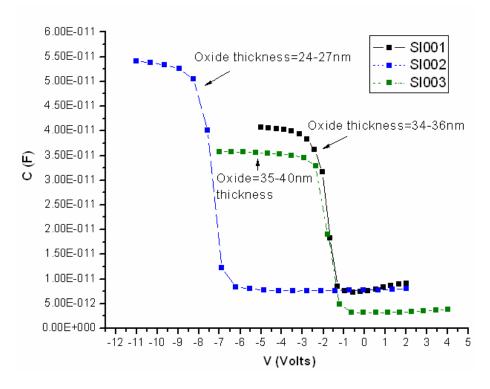

| 3.30 | C-V characteristics of MOSCAP 5 for SI001, SI002 and SI003 with different dielectric thicknesses |

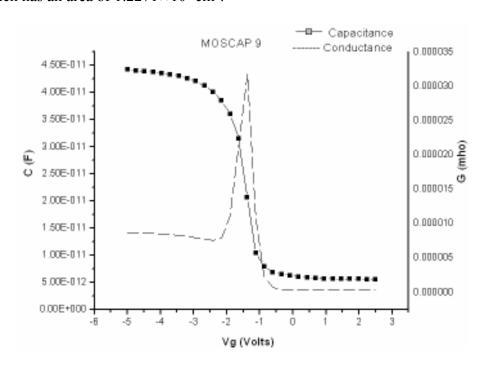

| 3 31 | C-V characteristics of MOSCAP 9 sample HK 008                                                    |

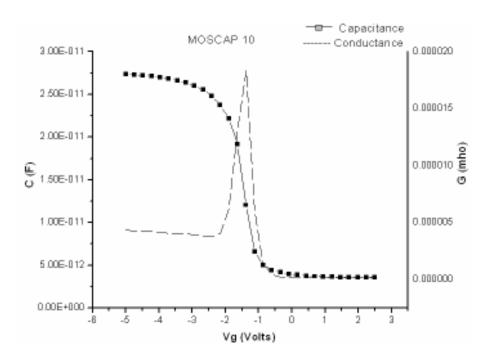

| 3.32 | C-V characteristics of MOSCAP 10, sample HK 008                                                   | 113 |

|------|---------------------------------------------------------------------------------------------------|-----|

| 3.33 | C-V characteristics of MOSCAP 5, sample HK 009                                                    | 117 |

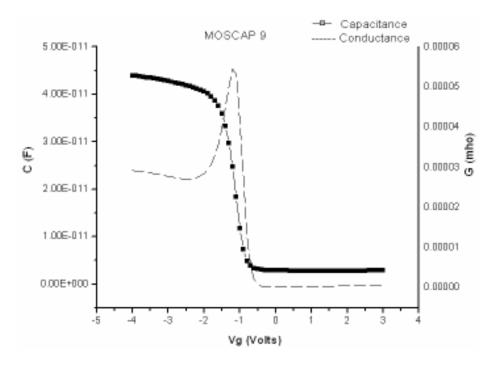

| 3.34 | C-V characteristics of MOSCAP 9, sample HK 009                                                    | 117 |

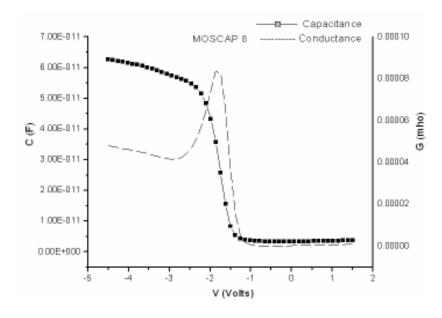

| 3.35 | C-V characteristics of MOSCAP 8, sample HK 010                                                    | 120 |

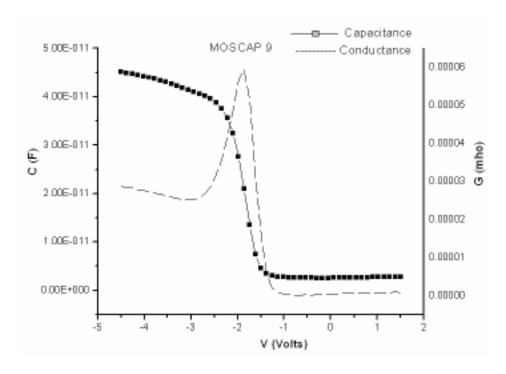

| 3.36 | C-V characteristics of MOSCAP 9, sample HK 010                                                    | 121 |

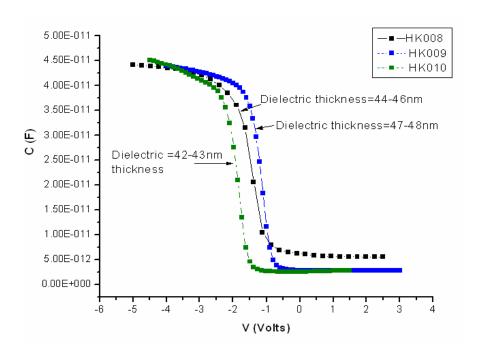

| 3.37 | C-V characteristics of MOSCAP 5 for HK008, HK009 and HK010 with different dielectric thicknesses. | 124 |

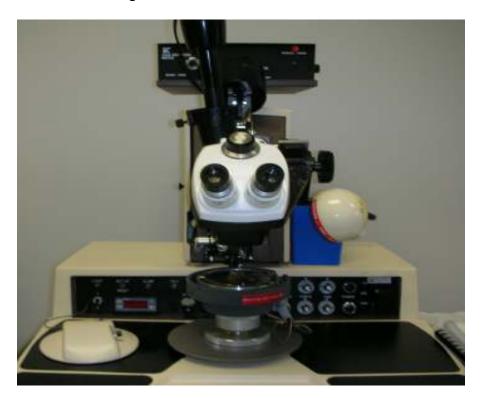

| 4.1  | Kulicke & soffa thermo sonic ball bonder                                                          | 129 |

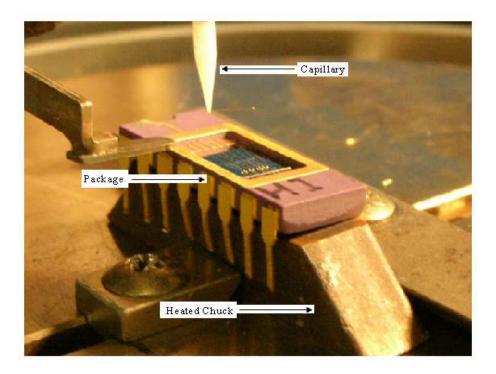

| 4.2  | DIP package on heated chuck                                                                       | 130 |

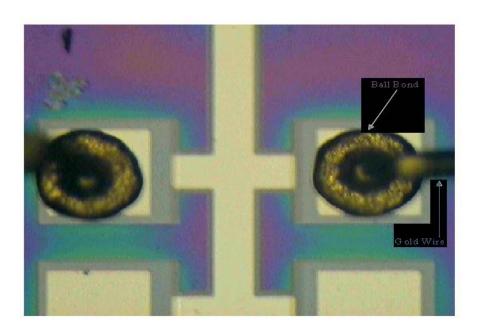

| 4.3  | Ball bond on Hall-Bar pads                                                                        | 131 |

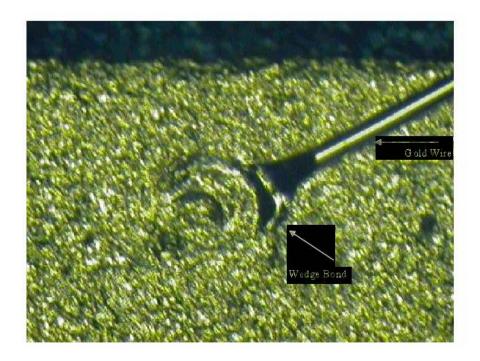

| 4.4  | Wedge bond on sample.                                                                             | 131 |

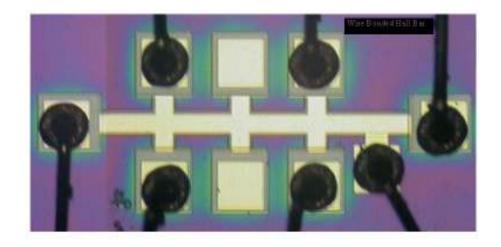

| 4.5  | Wire bonded Hall-bar with ball bonds on its pads                                                  | 132 |

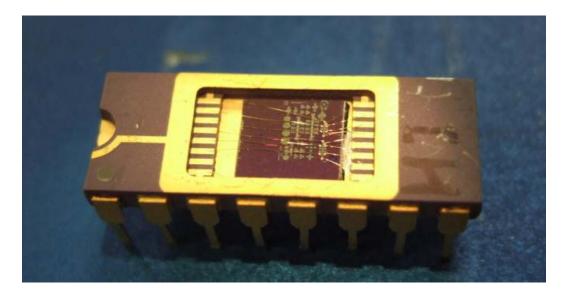

| 4.6  | Wire bonded chip on a DIP package.                                                                | 132 |

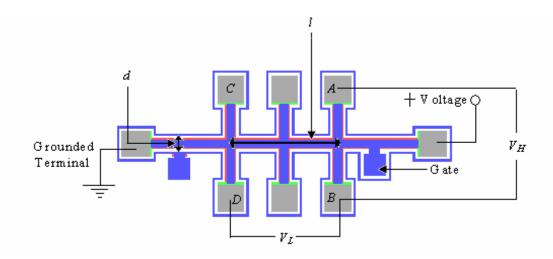

| 4.7  | Schematic diagram with various parameters used for Hall mobility measurements.                    | 135 |

| 4.8  | Hall mobility measurement setup                                                                   | 137 |

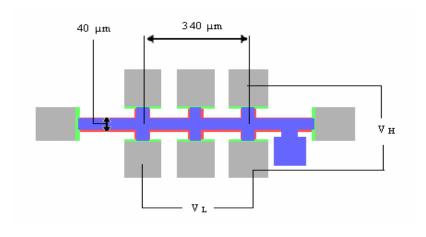

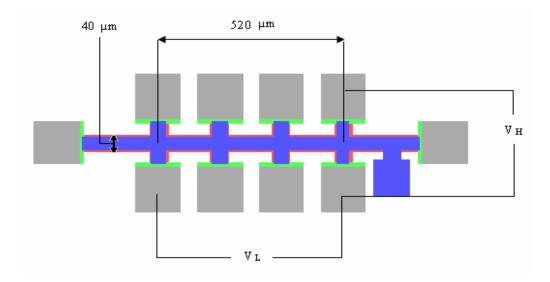

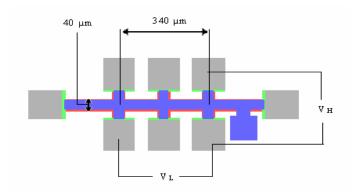

| 4.9  | Device under analysis on Sample S-20, Hall-Bar 2                                                  | 139 |

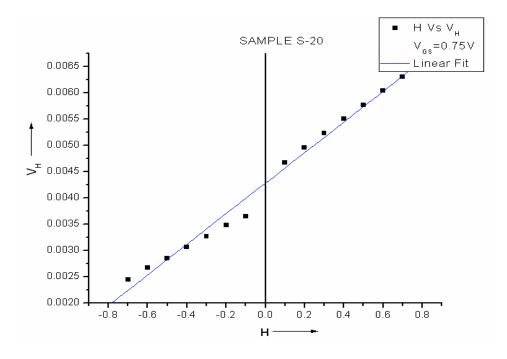

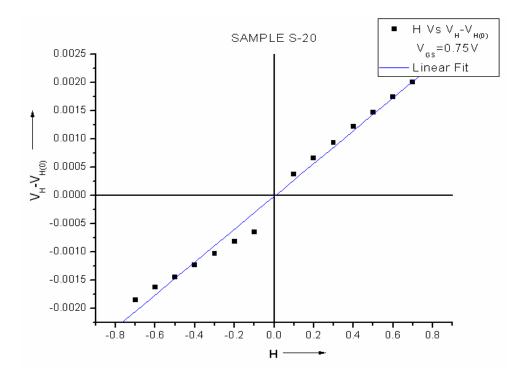

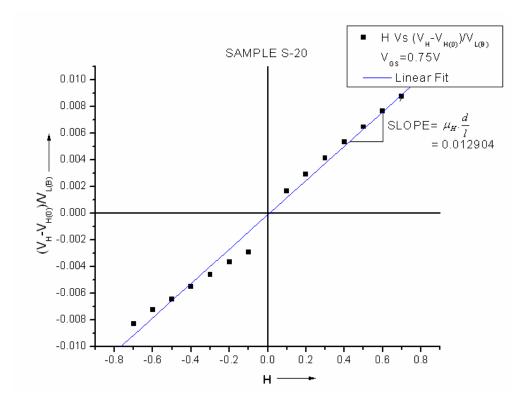

| 4.10 | $V_H$ Vs H at $V_g = 0.75$ V for S-20                                                             | 140 |

| 4.11 | $V_{\text{H}}\text{-}V_{\text{H}(0)}$ Vs H at $V_{\text{g}}$ = 0.75V for S-20                     | 141 |

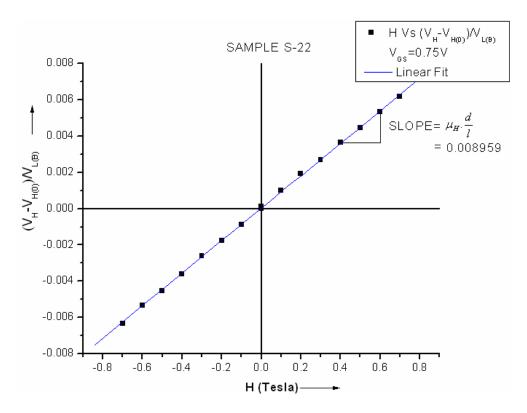

| 4.12 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_g = 0.75V$ for S-20                                        | 142 |

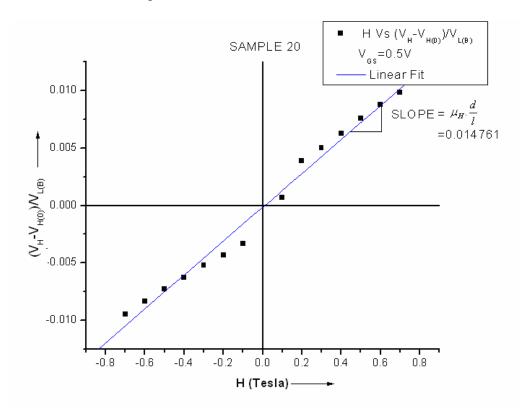

| 4.13 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_g = 0.5V$ for S-20                                         | 143 |

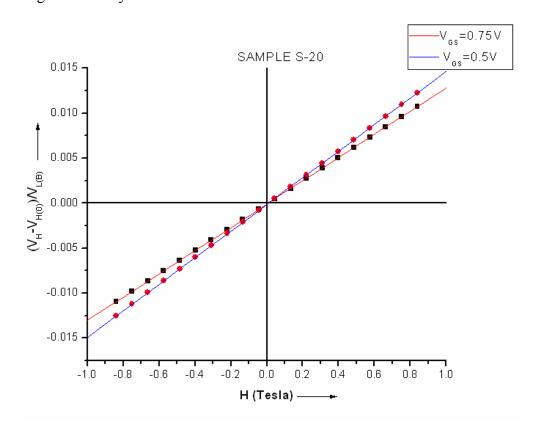

| 4.14 | Comparison of $(V_H-V_{H(0)})/V_{L(B)}$ Vs H for S-20 at $V_g$ =0.5V and $V_g$ =0.75V             | 144 |

| 4.15 | Device under analysis on Sample S-21, Hall-Bar 1                                                                                       | 145 |

|------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

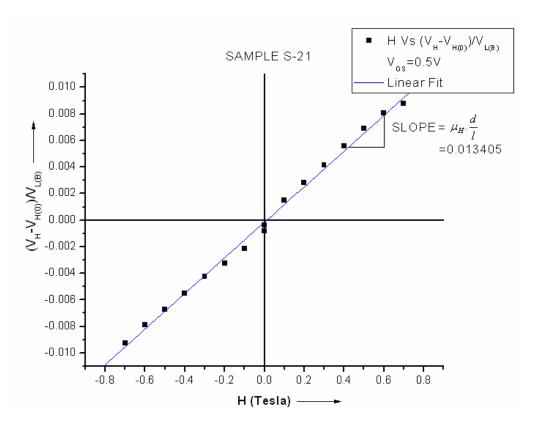

| 4.16 | $(V_H-V_{H(0)})/V_{L(B)}$ Vs H at $V_g=0.5V$ for S-21                                                                                  | 146 |

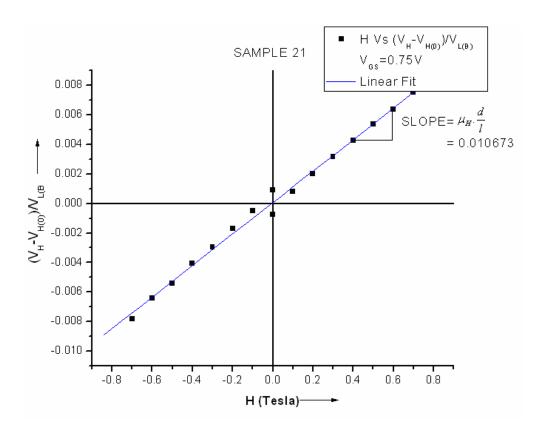

| 4.17 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_g = 0.75V$ for S-21                                                                             | 147 |

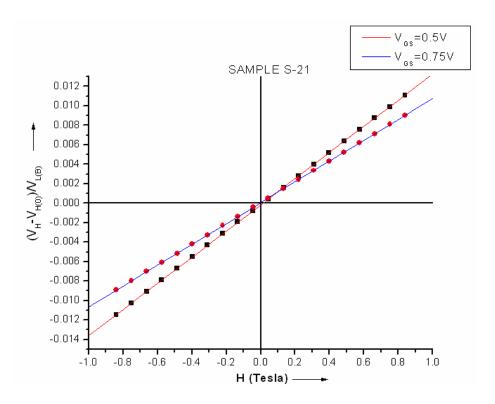

| 4.18 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for S-21 at V <sub>g</sub> =0.5V and V <sub>g</sub> =0.75V. | 148 |

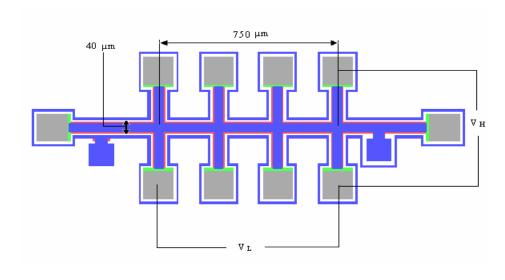

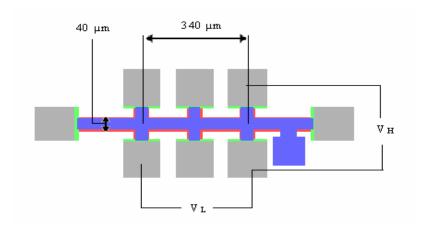

| 4.19 | Device under analysis on Sample S-22, Hall-Bar ring 1                                                                                  | 148 |

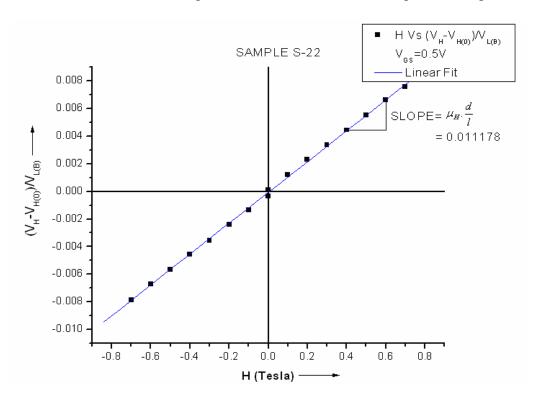

| 4.20 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_{g}=0.5V$ for S-22                                                                              | 149 |

| 4.21 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_g = 0.5V$ for S-21                                                                              | 150 |

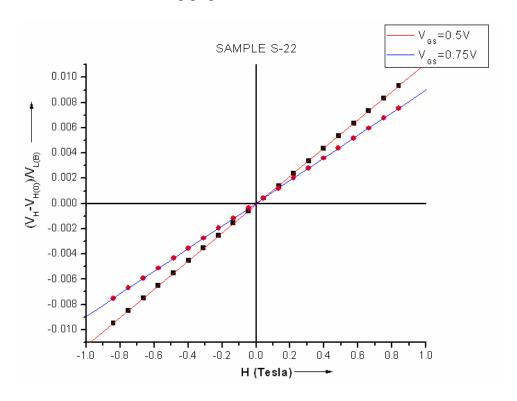

| 4.22 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for S-22 at V <sub>g</sub> =0.5V and V <sub>g</sub> =0.75V. | 151 |

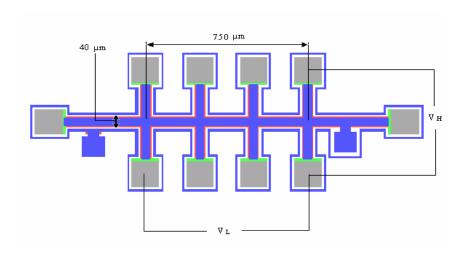

| 4.23 | Device under analysis on Sample S-24, Hall-Bar 2                                                                                       | 151 |

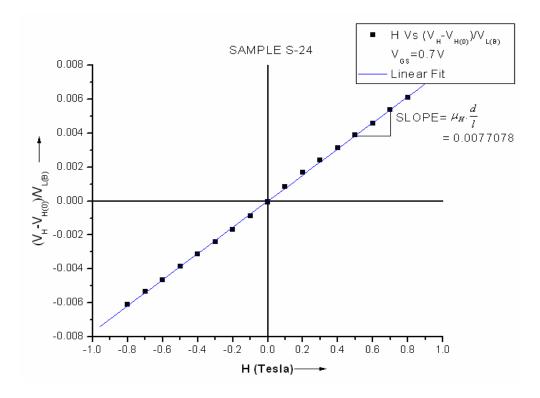

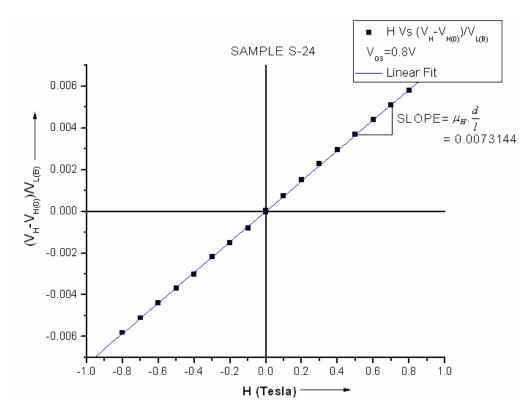

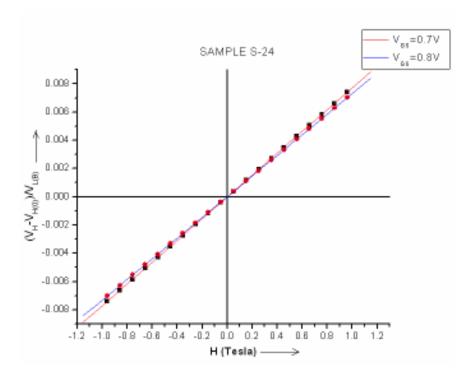

| 4.24 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_{g}=0.7V$ for S-24                                                                              | 152 |

| 4.25 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_{g}=0.8V$ for S-24                                                                              | 153 |

| 4.26 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for S-24 at V <sub>g</sub> =0.7V and V <sub>g</sub> =0.8V   | 154 |

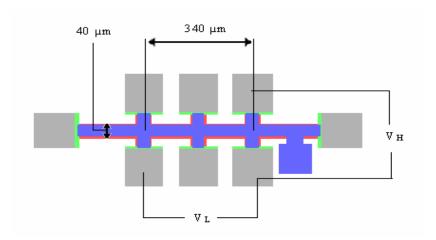

| 4.27 | Device under analysis on Sample S-26, Hall-Bar ring 1                                                                                  | 154 |

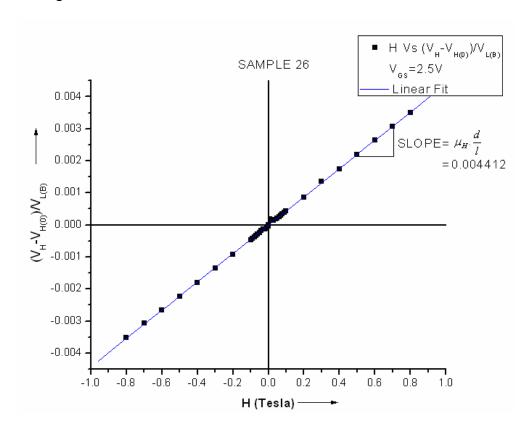

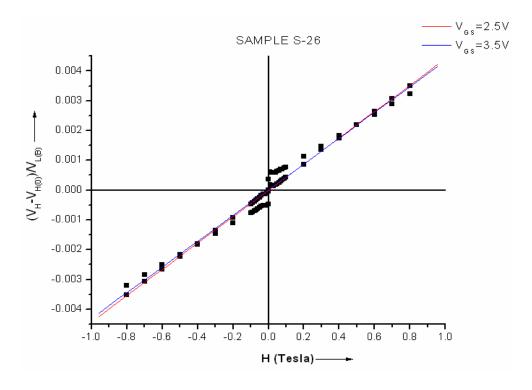

| 4.28 | (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H at V <sub>g</sub> = 2.5V for S-26                                         | 155 |

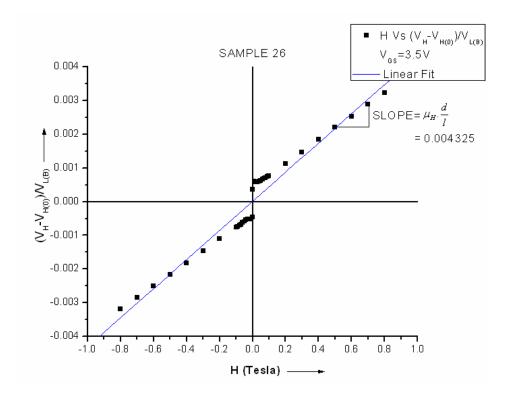

| 4.29 | $(V_H-V_{H(0)})/V_{L(B)}$ Vs H at $V_g=3.5V$ for S-26                                                                                  | 156 |

| 4.30 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for S-24 at V <sub>g</sub> =2.5V and V <sub>g</sub> =3.5V.  | 157 |

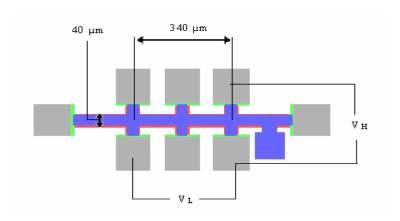

| 4.31 | Device under analysis on Sample S-28, Hall-Bar 2                                                                                       | 158 |

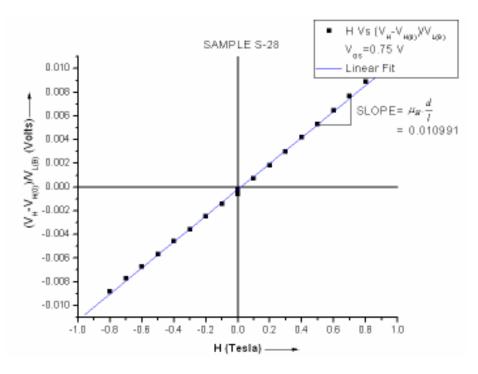

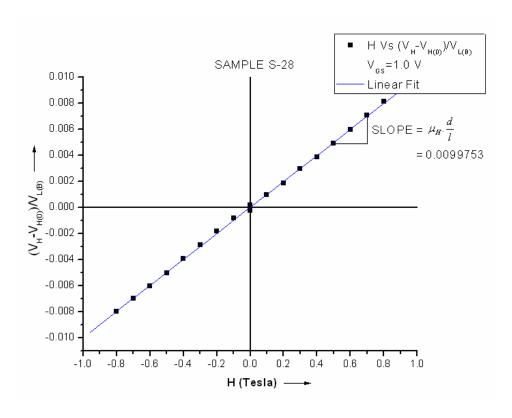

| 4.32 | (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H at V <sub>g</sub> = 0.75 V for S-28                                       | 158 |

| 4.33 | $(V_H-V_{H(0)})/V_{L(B)}$ Vs H at $V_g=1.0V$ for S-28                                                                                  | 159 |

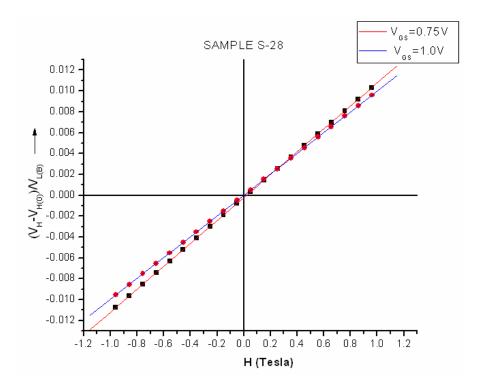

| 4.34 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for S-28 at V <sub>g</sub> =0.75V and                       |     |

|      |                                                                                                                                        |     |

|      | $V_g = 1.0V$                                                                                                                         | 160   |

|------|--------------------------------------------------------------------------------------------------------------------------------------|-------|

| 4.35 | Device under analysis on Sample H-3, Hall-Bar 2.                                                                                     | 162   |

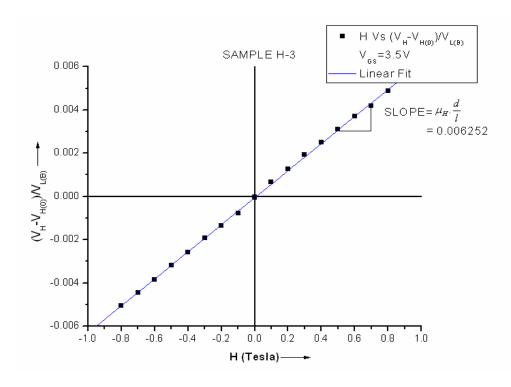

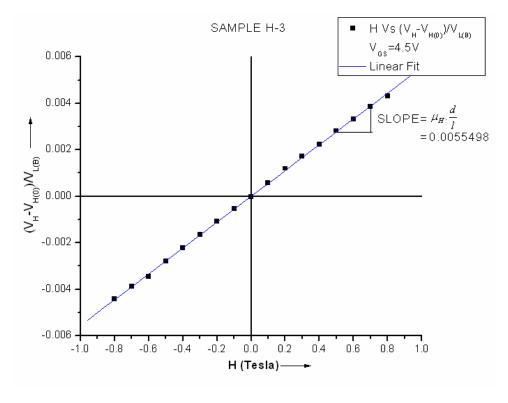

| 4.36 | $(V_H-V_{H(0)})/V_{L(B)}$ Vs H at $V_g=3.5V$ for H-3                                                                                 | 162   |

| 4.37 | $(V_H-V_{H(0)})/V_{L(B)}$ Vs H at $V_g=4.5V$ for H-3                                                                                 | 163   |

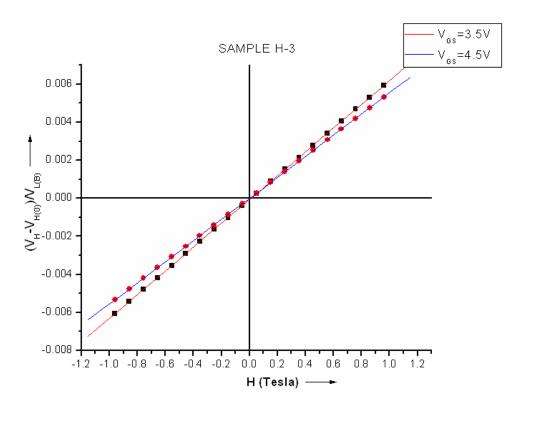

| 4.38 | Comparison of (V <sub>H</sub> -V <sub>H(0)</sub> )/ V <sub>L(B)</sub> Vs H for H-3 at V <sub>g</sub> =3.5V and V <sub>g</sub> =4.5V. | 164   |

| 4.39 | Device under analysis on Sample H-4, Hall-Bar 2                                                                                      | 165   |

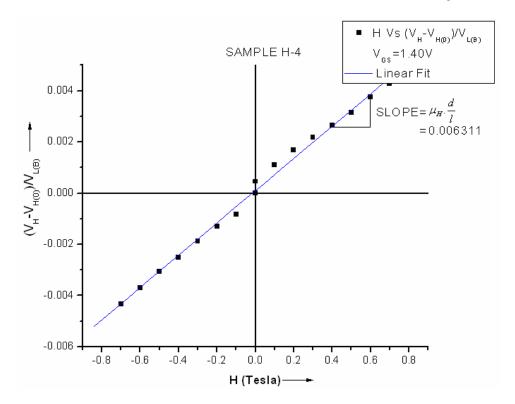

| 4.40 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_{g} = 1.40V$ for H-4                                                                          | 165   |

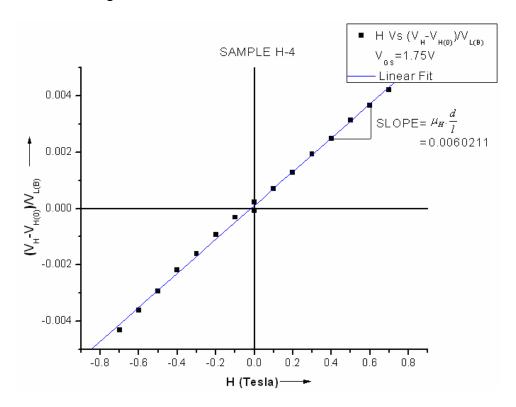

| 4.41 | $(V_{H}-V_{H(0)})/V_{L(B)}$ Vs H at $V_{g} = 1.75V$ for H-4                                                                          | 166   |

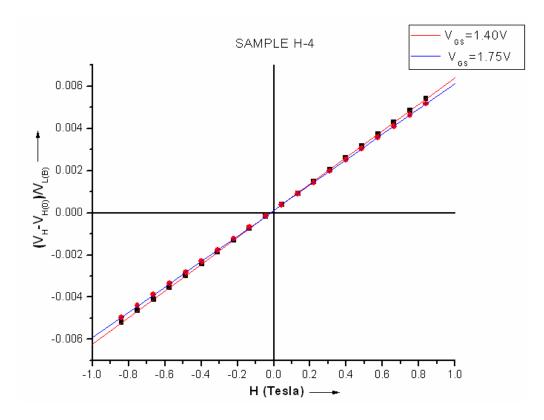

| 4.42 | Comparison of ( $V_H$ - $V_{H(0)}$ )/ $V_{L(B)}$ Vs H for H-4 at $V_g$ =1.4V and $V_g$ =1.75V.                                       | . 167 |

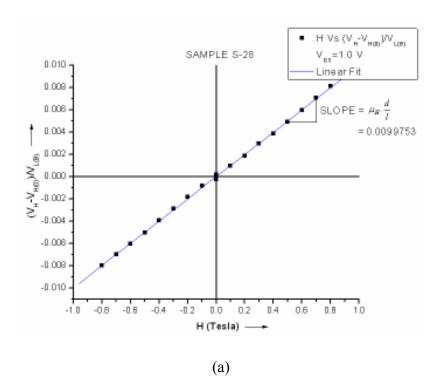

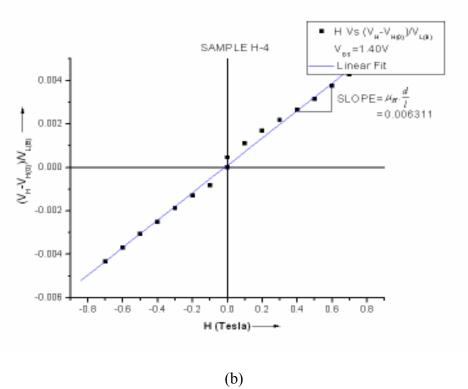

| 4.43 | Comparison of $\mu_H(d/l)$ for (a) S-28 and (b) H-4                                                                                  | 169   |

# LIST OF TABLES

| Tabl | Γable                                                              |      |

|------|--------------------------------------------------------------------|------|

| 1.1  | Roadmap for technology and equivalent dielectric thickness         | 4    |

| 3.1  | Summary of I-V results of SiO <sub>2</sub> based samples.          | . 91 |

| 3.2  | Summary of I-V results of HfSiO based samples.                     | . 98 |

| 3.3  | Comparison between SiO <sub>2</sub> and HfSiO based samples        | . 98 |

| 3.4  | Summary of C-V results of SiO <sub>2</sub> based samples.          | 111  |

| 3.5  | Summary of C-V results of HfSiO based samples.                     | 125  |

| 4.1  | Wire bonding parameters                                            | 133  |

| 4.2  | Summary of Hall mobility results of SiO <sub>2</sub> based samples | 161  |

| 4.3  | Summary of Hall mobility results of HfSiO based samples            | 168  |

| 4.4  | Comparison of Hall mobilities of S-28 and H-4                      | 170  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Historical Perspective

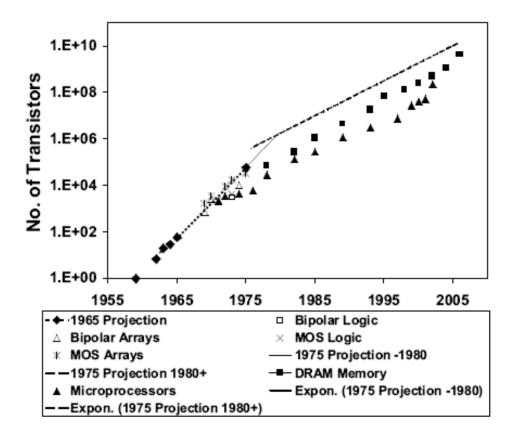

The invention of Field Effect Transistor (FET) and the further development of silicon based integrated circuit fabrication techniques have led to unprecedented levels of growth in the semiconductor industry in the past decades. In the past years the scaling of transistor to smaller and smaller dimensions has led to a phenomenal improvement in the device performance thereby resulting in the widespread usage of these microelectronic devices in our day-to-day lives. This shrinkage of component size and subsequent increase in the number of components on the chip was first predicted by Gordon E. Moore [1] in 1965 and was predicted to last a decade. Beginning in 1975 this slope changed to doubling every 18 months or a fourfold increase every three years. This trend came to be known as Moore's law and is still the central guide to the semiconductor industry. With exceptional developments in processing techniques, mainly in photolithography, Moore's law has proved its validity well into the 21st century. Moore's law has yet to be violated but fundamental thermodynamic limits are being reached in critical areas and innovative changes need to be made both in basic transistor materials and device structures so that the current rate of improvement can be maintained [2]. Moore's law of scaling is shown in Fig. 1.1 which clearly demonstrates the vision of Dr. Moore as far as the scaling of the device dimensions is concerned.

Figure 1.1 Moore's law of scaling. [1, 3]

The phenomenal progress signified by Moore's law has been achieved mainly through scaling of metal-oxide-semiconductor field-effect transistor (MOSFET) from larger physical dimensions to smaller physical dimensions, hence gaining density and speed [4]. This has further improved the performance-to-cost ratios for microelectronic devices thereby increasing their consumption in day to day life. Shrinking of conventional MOSFET beyond the 50 nm technology node requires certain innovations to bridge barriers which arise due to fundamental physics that constrains a conventional MOSFET. Some of these limits are 1) quantum mechanical tunneling of carriers through thin gate oxide i.e. SiO<sub>2</sub> in conventional MOSFETs; 2) quantum mechanical tunneling of carriers from source to drain and from drain to the body of the MOSFET;

3) control of the density and location of dopant atoms in the MOSFET channel and source/drain region to provide a high on-off current ratio; 4) the finite sub-threshold slope [4]. It was believed that optical lithography, which is used as the major patterning technique for conventional MOS fabrication, would reach its limits and it will limit the scaling of the devices. But SIA Roadmap [5] suggests that 130 nm deep UV optical lithography would be available for production of 0.1 µm devices. And even if this limit is reached and surpassed, X-ray and e-beam lithography would be introduced into MOS device manufacturing. So it is very unlikely that the scaling of the devices will be obstructed by the limits of lithography [6]. The thinning down of SiO<sub>2</sub> based gate dielectric material is the main cause of concern for the semiconductor industry today.

Silicon Dioxide has been used as the primary gate dielectric material in field effect devices since 1957 [7]. At first single devices were made and then integrated devices were made, and the thickness of SiO<sub>2</sub> decreasing with every passing generation. For the high-performance processors that are being process presently, the SiO<sub>2</sub> thickness has reached the value of 1.5 nm. Table 1.1 demonstrates the time line for the reduction lithography and equivalent dielectric thickness. The table displays with clarity the limits that are being touched by the scaling of device size in terms of minimum feature size and the role that is played by equivalent oxide thickness in this scaling.

Table 1.1 Roadmap for technology and equivalent dielectric thickness [5]

| Production year | Minimum feature size (μm) | Equivalent dielectric |

|-----------------|---------------------------|-----------------------|

|                 |                           | thickness (A)         |

| 1997            | 0.25                      | 40-50                 |

| 1999            | 0.18                      | 30-40                 |

| 2001            | 0.15                      | 20-30                 |

| 2003            | 0.13                      | 20-30                 |

| 2006            | 0.10                      | 15-20                 |

| 2009            | 0.07                      | <15                   |

| 2012            | 0.05                      | <10                   |

Equivalent oxide thickness is the thickness of any dielectric material scaled by the ratio of its dielectric constant to the dielectric constant of silicon dioxide ( $\varepsilon_{oxide}$ =3.9) [7]. Such that

$$t_{x} = t_{eq} \frac{\varepsilon_{x}}{\varepsilon_{oxide}} \tag{1.1}$$

Where  $t_x$  and  $t_{eq}$  are the physical thickness and the equivalent oxide thickness respectively, and  $\varepsilon_{oxide}$  and  $\varepsilon_x$  are the dielectric constants of silicon dioxide and the other dielectric [7]. With reduction in the thickness of the conventional dielectric material SiO<sub>2</sub> below 1.5nm, the gate leakage currents through the dielectric increases and gives rise to manufacturing control and reliability issues in the manufacture of high performance devices. In order to reduce the leakage current and improve devices

reliability alternate dielectric materials came to be investigated as a prospective replacement to the conventional gate dielectric  $SiO_2$ . It was understood that the aforementioned issues related to  $SiO_2$  could be eliminated if new dielectric materials were used with higher dielectric constant. So using an alternative dielectric x, with  $\varepsilon_x > \varepsilon_{oxide}$ , a thicker layer could be used which would reduce the leakage current and improve device reliability. This led to the introduction and development of high-k dielectric materials. There are many materials that are being investigated in this category. But high- k dielectric materials have some disadvantages, which have served as a roadblock in their transition in becoming the gate dielectric material for high performance devices. One of the most important disadvantages of high-k dielectric materials is the reduction in channel carrier mobility.

This work discusses the fabrication, characterization and mobility analysis of indigenously fabricated MOS devices with both SiO<sub>2</sub> and high-k dielectric gate materials explaining the approach we have adopted to the problem of true mobility extraction of carriers in the transistor channel.

### 1.2 Theory of MOSFETS

Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is the fundamental building block of MOS and CMOS digital integrated circuit. The MOS transistor occupies a relatively smaller silicon area, and has fewer fabrication steps as compared to a bipolar junction transistor [8]. The power consumed by the MOSFET is less than BJTs, typically at lower frequencies [9]. Because of their simpler fabrication, lower power consumption and higher density, MOSFETs are widely used in memory

circuits, displacing the bipolar memories completely. The same advantages have led to the domination of MOSFETs for logic circuits too, especially in high speed microprocessors [9]. The high volume of production of MOSFETs integrated circuits has financed research programs to improve the performance of the MOSFET. The main ongoing research is to reduce the device size, allowing more devices on a chip and improve the frequency response.

## 1.2.1 Structure of MOSFET

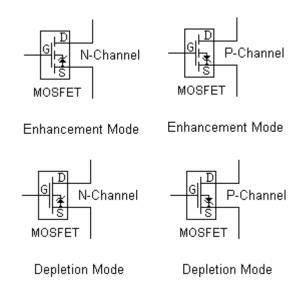

The MOSFET is a four-terminal device. The two types of MOSFETs are n-channel (in which conducting carriers are electrons) and p-channel (in which conducting carriers are holes). MOSFETS with different configurations are shown in Fig. 1.2 below.

Figure 1.2 Different kinds of MOSFETS [10]

It consists of a substrate, which is p-type in the case of an n-channel MOSFET, in which two n<sup>+</sup> diffused regions, the drain and the source are formed. The surface of the substrate region between the drain and the source is covered with a thin oxide layer and

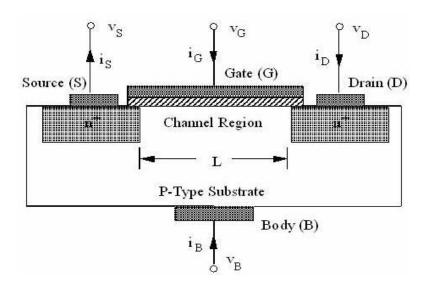

a metal or poly-silicon gate is deposited on top of this gate dielectric. n-channel MOSFETs are built on p-type silicon and p-channel MOSFETs are built on n-type silicon. In case of n-channel MOSFETs positive gate voltages of sufficiently high magnitudes create a conducting channel and for p-channel MOSFETs negative gate voltages of sufficiently high magnitudes create a conducting channel. In this work concentration will be focused on n-channel MOSFETs. The reason for explaining the n-channel MOSFET is due to the fact that it is more commonly used commercially [8] and hence we are also involved in the fabrication and analysis of n-channel MOSFETs and multi-drain Hall bars. The basic structure of an n-channel MOSFET is shown in Fig. 1.3 below.

1.3 Basic structure of an n-channel MOSFET [11]

The n-type source and drain regions are separated by a distance known as channel length L and the dimension perpendicular to the length is the channel width W. Both L and W are important parameters used to control the electrical properties of the

MOSFET [8]. The thickness of oxide  $x_{ax}$  covering the channel area just below the gate is a very important parameter too. The source and drain regions are electrically disconnected unless there is a conducting channel between them. This conducting channel is provided by the n-type inversion layer which is formed by the application of the gate voltage. When the inversion layer is formed and a voltage is applied between the source and drain regions, the carriers enter the channel from the source and depart from the drain, which results in current from drain to source in case of n-channel MOSFETs and source to drain in case of p-channel MOSFETs. We can fabricate the MOSFETs, which have an inversion layer at zero gate-to-source voltage ( $V_{gs}$ ). These kinds of MOSFETs are called *depletion-mode* MOSFETs. The drain current in these MOSFETs can be reduced by changing the gate-to-source voltage ( $V_{gs}$ ). MOSFETs in which inversion layer is not formed at  $V_{gs} = 0$  are called *enhancement-mode* MOSFETs. Enhancement-mode MOSFETs are more commonly used in circuits than depletion-mode MOSFETs [8, 9].

### 1.2.2 The MOS system under External Bias-Operating Modes of a MOSFET

There can be two controlling parameters for MOSFET operation. These are gate voltage  $(V_g)$  and substrate voltage  $(V_b)$ . In the analysis of electrical behavior of the MOSFET substrate voltage  $V_b = 0$  and the gate voltage  $V_g$  is the controlling parameter. With the polarity and magnitude of the gate voltage  $V_g$  three operating regions are observed in a MOSFET i.e. accumulation, depletion and inversion. We concentrate our analysis on n-channel MOSFETs here.

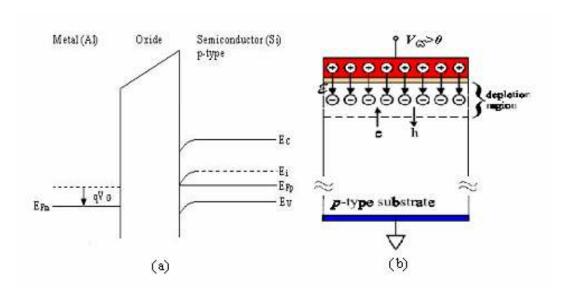

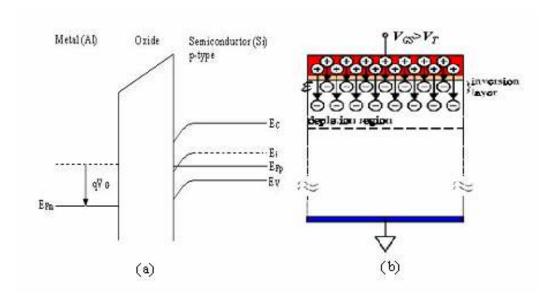

On application of negative gate voltage  $V_g$ , the holes, that are the majority carriers in the p-type substrate, come to the semiconductor-oxide interface. The majority carrier concentration near the surface exceeds the equilibrium concentration of majority carriers i.e. the holes in the substrate and this condition is knows as accumulation as this is caused by the carrier accumulation on the surface [8, 9]. The applied negative surface potential causes the energy bands to bend upward near the surface. This is demonstrated in the Figure 1.4 below. Due to the applied negative voltage the concentration of the holes increase near the surface but the concentration of the electrons decreases near the surface as the electrons are pushed deeper into the bulk of the substrate [8, 9].

Figure 1.4 Energy band diagram of MOS system operating in accumulation [8]

When a small positive gate voltage  $V_g$  is applied and the substrate bias being  $V_b$ =0, the electric field is directed towards the substrate in this case and hence the holes, which are the majority carriers, are pushed back into the substrate leaving behind negatively charged fixed acceptor ions. A depletion region is created near the surface

and the semiconductor-oxide interface is devoid of any mobile carriers. This is known as the depletion region of operation of a MOSFET. The positive gate bias causes the energy bands to bend downwards near the surface. This is demonstrated in the energy band diagram of depletion region operation in Fig. 1.5 below [8, 9].

Figure 1.5 a) Energy band diagram of a MOS system operating in depletion b) Cross-sectional view of MOS system operating in depletion [8]

The thickness of the depletion region is expressed as a function of the surface potential and bulk Fermi potential as

$$x_d = \sqrt{\frac{2.\varepsilon_{Si} \left| \phi_s - \phi_F \right|}{q.N_A}} \tag{1.2}$$

And the depletion charge density is given as

$$Q = -\sqrt{2q.N_A.\varepsilon_{Si}.|\phi_s - \phi_F|}$$

(1.3)

Where  $x_d$  is the depth of the depletion region, Q is the depletion region charge density,  $\phi_s$  is the surface potential,  $\phi_F$  is the bulk Fermi potential,  $N_A$  is the acceptor concentration and  $\varepsilon_{Si}$  is the dielectric coefficient of silicon [8].

If the positive gate bias is increased further the electrons from the bulk are attracted towards the surface and the electron density exceeds the majority hole density. As a result of this an n-type region is created near the surface and it is called the inversion layer and this phenomenon is called surface inversion. As a result of increasing surface potential the energy bands bend further downwards and eventually the mid-gap energy level  $E_i$  gets smaller than the Fermi level  $E_{Fp}$  on the surface concluding that the substrate semiconductor in this region becomes n-type. This is demonstrated in the energy band diagram shown below.

Figure 1.6 Energy band diagram of a MOS system operating in inversion b) Cross-sectional view of MOS system operating in inversion [8]

This inversion condition requires that the surface potential  $\phi_s$  has the same magnitude but different polarity as the bulk Fermi level  $\phi_F$  [8, 9]. On reaching the condition of surface inversion, there is no further increase in the depth of the depletion region. After that with the increase of the positive gate bias, only the mobile electron concentration increases. So the depletion region depth achieved at the onset of inversion is the maximum depth of the depletion layer [8]. With inversion condition  $\phi_s = -\phi_F$  the maximum depth of depletion layer is given by

$$x_{dm} = \sqrt{\frac{2.\varepsilon_{Si} |2\phi_F|}{q.N_A}}$$

(1.4)

Where  $x_{dm}$  is the maximum depth of depletion layer [8].

# 1.2.3 Threshold Voltage

The value of gate-to-source voltage  $V_g$  needed to cause surface inversion condition is called the threshold voltage  $V_{T0}$ . So  $V_g > V_{T0}$  for the conductance in the channel to take place. Threshold voltage is a very important parameter in the operation of MOSFET. As mentioned earlier at the onset of inversion  $\phi_s = -\phi_F$  so modifying equation (1.3) to use this condition [8]:

$$Q_{B0} = -\sqrt{2q.N_A.\varepsilon_{Si}.-2\phi_F}$$

(1.5)

But as the source is at a different potential than the substrate, the depletion region charge density can be expressed a function of source to substrate voltage  $V_{sb}$ .

$$Q_B = -\sqrt{2q.N_A.\varepsilon_{Si}.-2\phi_F + V_{sb}}$$

(1.6)

The component that offsets the depletion region charge is  $\frac{-Q_B}{C_{ox}}$  where  $C_{ox}$  the capacitance of the gate oxide per unit area is given as

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}} \tag{1.7}$$

There is always a fixed positive charge density  $Q_{ox}$  at the interface between gate oxide and the silicon substrate due to impurities and lattice imperfections. The gate voltage component to offset this component is  $\frac{-Q_{ox}}{C_{ox}}$  [8]. Combining all these factors the threshold voltage for zero substrate bias is given as

$$V_{T0} = \phi_{GC} - 2\phi_F - \frac{Q_{B0}}{C_{cr}} - \frac{Q_{ox}}{C_{cr}}$$

(1.8)

But  $V_{T0}$  is the threshold voltage for in case of zero-substrate bias. For threshold voltage in case of non-zero substrate bias

$$V_{T} = \phi_{GC} - 2\phi_{F} - \frac{Q_{B}}{C_{ox}} - \frac{Q_{ox}}{C_{ox}}$$

(1.9)

The final expression of threshold voltage [8] that is considered most widely is given as

$$V_T = V_{T0} + \gamma \cdot \left( \sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|} \right)$$

(1.10)

Where the parameter  $\gamma$  is known as the substrate bias coefficient [8] and is given as

$$\gamma = \frac{\sqrt{2q.N_A.\varepsilon_{Si}}}{C_{ox}} \tag{1.11}$$

The threshold voltage expression given in Eq. (1.10) can be used for both nMOS and pMOS devices. The difference would be the polarity in case of some of the perimeters. Specifically

- $\phi_F$  is negative in case of n-channel MOSFETS, positive in p-channel

- $Q_{B0}$  and  $Q_{B}$  are negative in n-channel MOSFETs, positive in p-channel

- $\gamma$  is positive in n-channel MOSFETs, negative in p-channel

- $V_{sb}$  is positive for n-channel MOSFETs, negative for p-channel

But typically the threshold voltage is negative for p-channel MOSFETs and positive for n-channel MOSFETs [8, 9].

#### 1.2.4 Gate Oxide

The thickness and the quality of the gate oxide are two of the most critical parameters, as these qualities strongly affect the operational characteristics of a transistor and also its long-term reliability [8, 9]. It can be recollected that the drain current [9] of a MOS transistor can be given by:

$$I_{d} = \mu.C_{ox}.\frac{W}{L}f(V_{ds}, V_{gs}, V_{T})$$

(1.12)

where  $\mu$  is the mobility of electrons in nMOS,

$C_{ox} = \varepsilon_{ox}/x_{ox}$  is the gate oxide capacitance per unit area,

W/L is the ratio of channel width to channel length and

$V_T$  is the threshold voltage of the transistor.

The above equation clearly indicates that the drain current is directly proportional to the gate oxide capacitance per unit area, which is inversely proportional to the gate oxide

layer thickness  $x_{ox}$ . Thus random fluctuations in  $x_{ox}$  can cause the corresponding variation in the drain current even under the same biasing conditions. These variations in the drain current can cause the variations in the circuit performances such as delay times, power consumption and logic threshold voltage [8, 9]. The function of the gate oxide is to provide a high-quality insulator between the conductive gate and the substrate. Although it prevents the current flow from the gate to the substrate, the oxide layer allows the penetration of electric field from gate to the substrate. The gate oxide in the MOS transistors is usually silicon dioxide SiO<sub>2</sub> or it can be Silicon Oxy-nitride SiON or silicon nitride Si<sub>3</sub>N<sub>4</sub> [4].

## 1.2.5 Carrier Mobility and Current Density

Carrier mobility ( $\mu$ ) is an important parameter in determining device performance in electronics. It is vital for describing the operation of semiconductor devices such as a MOS transistor [12]. It is one of the important input parameters for expressing electrical current in devices. The knowledge of carrier mobility is also important for knowing the doping level in wafers [12]. Here by carrier mobility we mean the electron mobility  $\mu_n$  and hole mobility  $\mu_p$ . As electrons are the majority carriers in nMOS devices, we are inclined towards the electron mobility analysis. Mobility is an important parameter for carrier transport as it describes how strong the motion of an electron or a hole is influenced by an applied electric field.

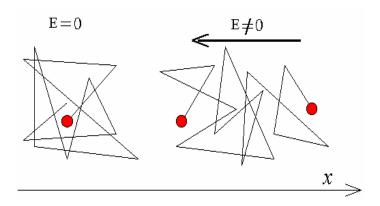

The electrons (or holes) in a semiconductor move rapidly in all directions at room temperature [13, 14]. In the absence of an applied electric field, the carrier exhibits random motion and carriers move quickly through the semiconductor and

frequently changes direction. When an electric field is applied, the random motion still occurs but in addition to that, there is on an average motion along the direction of the field. Due to their different electronic charge, holes move on in the direction of the electric field while electrons move in the opposite direction [13]. This phenomenon is shown is Fig. 1.7 below

Figure 1.7 Random motion of carriers in a semiconductor with and without applied electric field [13].

The random motion of electrons leads to zero net displacement of an electron over a sufficiently long period of time. The average distance between collisions is called the mean free path and the average time between collisions is called the mean free time ( $\tau_c$ ). For the typical value of  $1 \times 10^{-5}$  cm mean free path, the mean free time( $\tau_c$ ) is about 1 ps ( $\sim 10^{-12}$  s) [14]. On application of a small electric field (E) on the semiconductor sample, each electron experiences a force –qE along the field (in the opposite direction of the field) between collisions. Hence an additional velocity component is superimposed upon the thermal motion of electrons called drift velocity ( $\nu_n$ ). So the net displacement of the electrons is in the direction opposite to applied field due to combined effect of drift velocity and random thermal motion. The electron drift velocity

is proportional to the applied electric field. The proportionality factor depends on the mean free time and the effective mass. This proportionality factor is the electron mobility (or hole mobility) in the units of cm<sup>2</sup>/V-s given as [14]

$$\mu_n = \frac{q\langle \tau_c \rangle}{m^*} \tag{1.13}$$

where  $\mu_n$  is the electron mobility,

q is the charge on a electron,

$\tau_c$  is the mean free time and

$m^*$  is the effective mass of the electron.

Hence

$$v_n = -\mu_n . E \tag{1.14}$$

where  $v_n$  is the drift velocity of the electrons. The negative sign is used in the Eq. (1.14) as the electrons drift in the direction opposite to the Electric field E. A similar expression for hole mobility is given by

$$v_p = \mu_p.E \tag{1.15}$$

where  $v_p$  is the drift velocity of the holes,  $\mu_p$  is the hole mobility and E is the applied electric field. The negative sign is not incorporated in the equation as the holes drift in the same direction as the electric field [14].

The current density (*J*) at low fields [14] due to conduction by drift therefore can be written in terms of electron and hole drift velocities,  $v_n$  and  $v_p$  as

$$J = q.n.v_n + q.p.v_p (1.16)$$

At high fields scattering limits the velocity to the maximum value and the relationship given above ceases to hold any importance. This is termed as velocity saturation [14]. The expression for J in terms of mobility  $\mu$  can be written as

$$J = (q.n.\mu_n + q.p.\mu_p)E \tag{1.17}$$

The first term in the above expression is the conductivity  $\sigma$ , in  $(\Omega cm)^{-1}$  and it is the inverse of the resistivity  $\rho$  [8]. So the above expression can be written in the form of conductivity and resistivity as

$$J = \sigma \cdot E = (1/\rho) \cdot E \tag{1.18}$$

#### 1.3 Channel Mobility Degradation Mechanisms in a MOSFET

The inversion layer mobility in MOSFETs has been a very important physical quantity that is a parameter used to describe the drain current and a probe to study the electrical properties of the two-dimensional carrier system [15]. But a comprehensive understanding of inversion layer mobility, which includes the quantitative description near room temperature, the effect of substrate doping, the difference between electron and hole mobility and the effect of surface orientation is of paramount importance. Takagi et. al describe effective normal field by the equation [15]

$$E_{eff} = (q / \varepsilon_{Si})(N_{dp1} + \eta.N_s)$$

(1.19)

where q is the elementary charge,  $\varepsilon_{Si}$  is the permittivity of silicon,  $N_{dpl}$  is the surface orientation of the depletion charge,  $N_s$  is the surface inversion carrier concentration. Here  $\eta$  is the key parameter in defining the effective normal field and in order to

provide a universal relationship, the value of  $\eta$  should be  $\frac{1}{2}$  for electron mobility and  $\frac{1}{3}$  for hole mobility. Effective normal field can also be expressed as

$$E_{ff} = \frac{1}{\varepsilon_{Si}} (\eta \cdot Q_{inv} + Q_B)$$

(1.20)

where  $\varepsilon_{Si}$  is the permittivity of silicon,  $Q_{inv}$  is the inversion layer charge and  $Q_B$  is the bulk depletion layer charge [16]. There are various factors that influence inversion layer mobility of carriers in a MOS transistor which include temperature, surface roughness, oxide quality and surface orientation of the Silicon wafer [15, 17]. With the scaling there is reduction in inversion layer mobility and this further reduces the current density. The various mechanisms responsible for the degradation in inversion layer mobility will be discussed in detail in the sections 1.3.1 and 1.3.2.

## 1.3.1 Charge Scattering Mechanisms

There are several scattering mechanisms inherent in the gate oxide. Scattering of inversion layer electrons (in n-MOS) at the oxide semiconductor interface is one the major source of mobility degradation in MOSFETs [18]. The relative importance of the scattering mechanisms depends on the operating temperature and strength of the surface electric field. According to equation B the mobility of electrons in the inversion layer is given by

$$\mu_n = \frac{q\langle \tau_c \rangle}{m^*} \tag{1.21}$$

where  $\mu_n$  is the electron mobility, q is the charge on a electron,  $\tau_c$  is the mean free time and  $m^*$  is the effective mass of the electron [14]. So the mobility is directly related to

mean free time between collisions, which in turn is determined by the scattering mechanisms [14]. Some of the main scattering mechanisms are discussed here.

A) Phonon Scattering: Lattice scattering is a result of the thermal vibrations of the lattice atoms at any temperature above the room temperature. The lattice periodic potential is disturbed by these vibrations and it allows the energy to be transferred between the lattice and the carriers. With increase in the temperature the lattice vibration increases. Consequently lattice scattering becomes dominant at high temperatures, thereby reducing the mobility at higher temperatures [14]. The allowed vibrational motions, which interact with the free electrons, are termed phonons. Scattering by acoustic phonon is called the *phonon scattering* and is found to limit the mobility in semiconductors at room temperatures. This scattering increases with the increase in the temperature. The acoustic phonons have the energies of approximately 0.05 eV. The mobility due to acoustical phonon scattering  $\mu_L$  decreases with increase in temperature as  $T^{-3/2}$  [14, 19]. So phonon scattering is important at room temperature and can be ignored at very low temperatures [19].

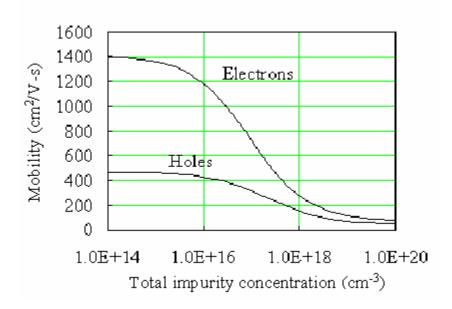

From Eq. (1.21) it can be observed that carrier mobility is inversely proportional to the effective mass. Hence, a larger mobility is expected with a carrier with smaller effective mass. Electron effective mass is smaller than the hole effective mass  $m *_n < m *_p$  [12]. At a given impurity concentration, the electron mobility exceeds the hole mobility  $\mu_n > \mu_p$  [12, 14]. This is demonstrated in the Fig. 1.8.

Figure 1.8 Electron and hole mobility versus doping density for silicon [13]

B) <u>Coulomb Scattering</u>: Ionized impurity scattering occurs when a charge carrier travels past an ionized dopant impurity, either a donor or an acceptor. The charge carrier path will be deflected due to Coulomb force interaction. The probability of impurity scattering depends on the total concentration of the ionized impurities, which is the sum of the concentration of negatively and positively charged ions. So as the Coulomb interaction is involved here, hence the name Coulomb scattering [14]. Coulomb scattering is basically due to charge centers, including fixed oxide charges, interface state charges and localized charge due to ionized impurities [19, 20]. Along with the Coulomb scattering these charges also have trapping effects [12, 14], which will be discussed in detail in the next section. The Coulomb scattering by substrate impurity is considered to degrade the mobility on higher impurity concentration substrates [15, 21]. However, unlike lattice scattering, impurity scattering becomes less a significant at

higher temperatures. This is because of the reason that the carriers move rapidly at higher temperatures and remain near the impurity center for a very short time. Hence there is less time for the Coulomb interaction to take place. This reduces the Coulomb scattering at higher temperature. The mobility near the room temperature due to ionized impurity scattering or Coulomb scattering varies with temperature and ionized impurity concentration  $N_I$ . This is given as  $T^{3/2}/N_I$ . So Coulomb scattering is an important consideration at lightly inverted surfaces. High surface charge densities or substrate doping concentration imply increase in Coulomb scattering. Coulomb scattering becomes less effective at heavily inverted surfaces due to carrier screening [19].

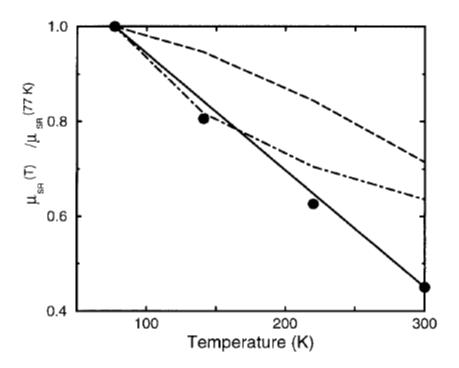

C) <u>Surface roughness scattering</u>: This scattering mechanism refers to the roughness at the Si-SiO<sub>2</sub> interface [19, 22, 24]. Popular analysis of surface roughness scattering suggests usually assume that mobility due to surface roughness scattering is temperature independent [15]. But from a physical standpoint carrier screening is supposed to give it some temperature dependence [23]. The mobility due to surface roughness scattering varies with temperature as  $T^{-1/3}$ . Surface roughness has the maximum impact on the mobility at low temperatures. The surface roughness scattering is important under strong inversion conditions as the distance of carriers from the surface governs the strength of the interaction. The closer the carriers are to the surface, the stronger the scattering due to surface roughness will be [19, 25].

Figure 1.9 Temperature dependence of the surface roughness limited mobility [23]

The total mobility is usually assumed to be related in a reciprocal manner to the individual contributions as

$$\frac{1}{\mu} = \frac{1}{\mu_{ph}} + \frac{1}{\mu_c} + \frac{1}{\mu_{sr}} \tag{1.22}$$

where  $\mu_{ph}$  is the mobility due to phonons,  $\mu_c$  is the mobility due to coulomb scattering and  $\mu_{sr}$  is the mobility due to surface roughness [16].

# 1.3.2 Charge Trapping Mechanisms

The understanding of the influence of charge within the oxide and at the oxide-silicon interface is very important. The presence of these charges is unavoidable in practical systems. These charges can cause various changes in the characteristics of the device, most importantly altering the threshold voltage and the flatband voltage [9]. In

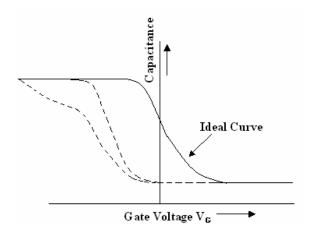

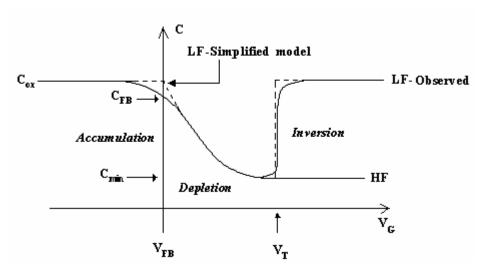

some cases the applied voltage influences these charges. In this case the threshold voltage depends on the gate voltage. The capacitance-voltage curve is then distorted as shown in the figure below.

Figure 1.10 Fixed charge effects on the capacitance-voltage curve of a MOS system [9]

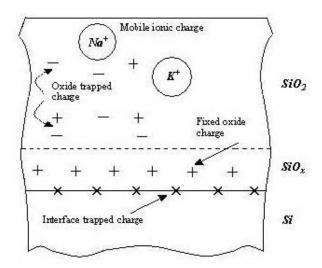

There are four distinct types of charges in the oxide-Silicon system. These four different types of charges are shown below in Fig. 1.11 below. These charges are located on different locations of the oxide-silicon system.

Figure 1.11 Four categories of oxide charges in a MOS system [9]

- A) Interface trapped charge: This is a positive charge and is located in a very thin (<1 nm) transition layer of non-stoichiometric silicon oxide  $SiO_x$ . The trapping levels are located at the oxide-silicon interface and have the energy levels within the forbidden gap between the valence band and the conduction band. They are distributed over energies within the energy gap. Clean surfaces have extra-allowed energy levels different from those in the bulk of the crystal. The inevitable presence of crystal defects and impurities introduced during processing add to more energy levels. Electrons in these extra levels and ions associated with them contribute to the interface charge[9]. The density of interface trapping states can be reduced typically by annealing the oxidized silicon wafer in hydrogen or forming gas [9, 25].

- B) Fixed Oxide charge: The fixed charge is present at the interface and within the oxide. The fixed charge always present at the interface arises from incomplete Si-Si bonds. The density of atoms at the surface of the silicon crystal depends on the crystal orientation and therefore depends on the orientation of the wafer [9, 17]. As more bonds are broken in the transition from silicon wafer with orientation (111) to silicon dioxide than in the transition in case of a (100) silicon wafer, fixed charge density is higher when (111) is used. Due to this reason the all the commercial devices are fabricated on (100) and not (111) [17]. Fixed charge densities also depend on high temperature processing hence annealing at high temperature can reduce some bonds and reduce the fixed charge density [9]. Fixed charge at the interface and within the oxide changes the threshold voltage [26]. So high fixed charge densities can cause the threshold voltage to be very high for practical applications especially with reduced supply voltage. In most

practical MOS structures, the densities of other charge centers, like the interface-trapped charge, are much smaller than the fixed oxide charge densities [19]. For example interface states commonly exhibit densities at least an order of magnitude smaller than fixed charge densities, provided an appropriate thermal anneal (generally  $400-500^{\circ}$ C in an  $N_2$  or  $N_2/H_2$  ambient) in the fabrication sequence [19, 27].

C) Mobile ionic charge: These charges result from alkali-metal ions (like sodium and potassium) that are readily absorbed in silicon dioxide. The alkali ions are sufficiently mobile to drift in the oxide in low voltage application. Their stability increases with increasing temperature so their effect on flatband voltage is more severe on high temperatures [9]. As the metal ions are positively charges, negative gate voltage causes the ions to migrate in to the metal-oxide interface where they do not affect the flatband voltage. But positive gate voltage moves these charges to the oxide-silicon interface where their effect is maximum. These charges can be avoided by careful processing and by introduction of certain impurities that immobilize these impurities [28]. Some of these impurities that can immobilize these ionic charges are chlorine and chlorine compounds which can be introduced by processing to stabilize the MOS system [9, 28]. D) Oxide trapped charges: These charges are located in the traps distributed throughout the oxide layer. Only a small amount of oxide trapped charges are introduced during processing. This charge is fixed except under unusual conditions. These charges can be both positive and negative but are usually negative [9].

## 1.4 High-K Dielectric Materials as an Alternative to SiO<sub>2</sub>

For more than 15 years, the physical thickness of SiO<sub>2</sub> has been reduced aggressively in compliance with Moore's law for low power consumption, high performance CMOS applications [29]. This is because it requires high integrated circuit density, which has translated into higher density of transistors on the wafer [30]. The improved performance related with the scaling of the device dimensions can be associated with the following equation [30] as

$$I_D = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[ 2 \cdot \left( V_{gs} - V_{T0} \right) V_{ds} - V_{ds}^{2} \right]$$

(1.23)

where W is the width of the transistor channel, L is the length of the transistor channel,  $\mu_n$  is the mobility of carrier electron in the channel,  $C_{ox}$  is the capacitance density associated with the gate dielectric when underlying channel is in the inverted state,  $V_{gs}$  and  $V_{ds}$  are voltages applied to transistor gate and drain and  $V_{T0}$  is the threshold voltage [30]. The drain current  $I_d$  increases linearly with  $V_d$  and eventually saturates at  $V_{dsat}$ . To yield drain current as

$$I_D(sat) = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{gs} - V_{T0})^2$$

(1.24)

The term  $V_g$ - $V_{T0}$  is limited in the range of reliability and room operation constraints as  $V_g$  cannot be very high. Thus even in a simplified approximation, reduction in channel length or an increase in the gate dielectric capacitance can increase drain current  $I_{dsat}$ . One of the key elements that have allowed the successful scaling of SiO<sub>2</sub> is its excellent material and electrical properties like thickness uniformity and control growth with a low density of interface defects, excellent chemical and thermal

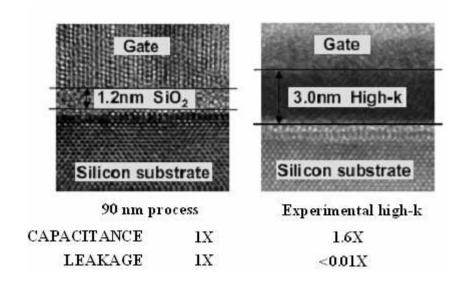

stability and large band gap which confers excellent isolation properties for it. But scaling beyond the present 1.2 nm range is an impediment in device scaling [31]. The first problem is the leakage current. This is because when the gate dielectric is very thin, the charge carriers can flow right through the gate insulator and this is called the quantum mechanical tunneling effect [31, 32]. This tunneling probability increases exponentially with the reduction in the thickness of the gate insulator. This results into an increase in the leakage current. Another issue can be the device reliability, as during the device operation carriers flow through the device, resulting in defects in the SiO<sub>2</sub> layer and the Si-SiO<sub>2</sub> interface. This can result in the breakdown of the dielectric and eventual breakdown of the device. Moreover the maximum gate voltage that can be applied to the device reduces with the thickness of the SiO<sub>2</sub> layer [33]. As temperature is increases some of the defect densities can increase high enough to cause a breakdown. All these limitations have prompted research for alternate gate dielectric materials, which can compensate for the scaling effects and help in the further scaling of the devices [30, 33].

If we just consider the gate capacitance, which is given as  $C = \frac{\kappa \cdot \mathcal{E}_0 \cdot A}{x}$  where k is the dielectric constant,  $\mathcal{E}_0$  is the permittivity of free space, A is the area of the capacitor and x is the thickness of the gate dielectric. The expression of C can be written in terms of  $x_{eq}$  and  $k_{ox}$ , which are the equivalent oxide thickness and dielectric constant of the capacitor respectively.  $x_{eq}$  is the thickness of SiO<sub>2</sub> that would be required to achieve the same capacitance density as the dielectric. So the physical thickness of an

alternative dielectric employed to achieve the equivalent capacitive density of  $x_{eq}$  can be obtained from the expression [33]

$$X_{high-\kappa} = \frac{\kappa_{high-\kappa}}{\kappa_{ox}} X_{eq}$$

(1.25)

So a gate dielectric with a higher dielectric constant affords a greater physical thickness and achieves the same capacitance as achieved by SiO<sub>2</sub> with lesser thickness. In other words by using high-k gate dielectric we can employ a thicker gate layer with lesser equivalent oxide thickness [30, 32, 33].

Figure 1.12 High-k for gate dielectrics [3]

Currently a wide range of materials are being investigated as an alternative to SiO<sub>2</sub> as gate dielectric material. Most of these materials are titanium (Ti) based e.g. TiO<sub>2</sub> [34], TiSi<sub>x</sub>O<sub>y</sub> [35], zirconium (Zr) based e.g. ZrO<sub>2</sub> [33, 34], hafnium (Hf) based e.g. HfO<sub>2</sub> [33, 34, 36, 37], HfSi<sub>x</sub>O<sub>y</sub> [35, 36, 38] and aluminum (Al) based e.g. Al<sub>2</sub>O<sub>3</sub> [34, 36]. The dielectric constants for these materials range from 9 (Al<sub>2</sub>O<sub>3</sub>) to 80 (TiO<sub>2</sub>)

[31]. There is also ultra high gate dielectric SrTiO<sub>3</sub> that has a dielectric constant 200 [31]. But it is not being investigated for the use in commercial devices. The dielectric constant of HfSi<sub>x</sub>O<sub>y</sub> is equal 8-15 depending upon the composition of Hafnium in the compound [31, 39].

Several methods of deposition are being investigated for the deposition of high-k materials on silicon. Plasma vapor deposition of HfO<sub>2</sub> followed by forming gas anneal [36], Atomic layer chemical vapor deposition using HfCl<sub>4</sub> and H<sub>2</sub>O and metal organic chemical vapor deposition of HfO<sub>2</sub> and HfSi<sub>x</sub>O<sub>y</sub> [33, 40], low temperature deposition of HfSi<sub>x</sub>O<sub>y</sub> by sputtering [39] and vapor-liquid hybrid deposition of Hafnium silicate films using Hf(OC<sub>4</sub>H<sub>9</sub>) and Si(OC<sub>2</sub>H<sub>5</sub>)<sub>4</sub> [41] are some of the methods that have been reported.

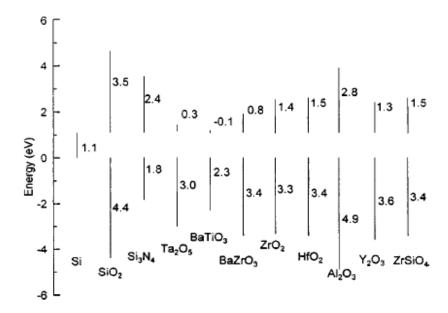

The high-k materials being investigated, though very promising, should fulfill some of the criteria that are important to their implementation as gate dielectric. Some of these criteria like permittivity, band structure and offset, thermodynamic stability, interface quality, film morphology, gate electrode compatibility, process compatibility and reliability should be addressed [42]. Fig. 1.13 demonstrates the conduction band and valence band offsets of various oxides on silicon.

Figure 1.13 Conduction band and valence band offsets of various oxides on Silicon [42]

Most importantly the high-k dielectric materials are required to meet the gate leakage requirements. Therefore the focus of efforts has shifted to Hafnium and Aluminum based dielectrics [33, 37]. These materials have the required thermodynamic and physical stability required for the integration with silicon substrate and metal/polysilicon gate during processing [37, 43]. Hafnium Silicate (HfSi<sub>x</sub>O<sub>y</sub>) is one potential candidate along with Hafnium oxide (HfO<sub>2</sub>) [39, 44]. Out of these two, HfO<sub>2</sub> has been a subject of very intense research. For thin gate dielectric candidates, the interface with the silicon channel plays a very important role in determining overall electrical properties. The thermal stability of refractory metal oxides such as TiO<sub>2</sub> has been investigated but they are not stable in contact with silicon and thus require an interfacial layer [34]. Though interface barriers have been developed between high-k and the silicon substrate, they comprise the gate stack capacitance since SiO<sub>2</sub> limits the

total capacitance of the stack. While HfO<sub>2</sub> has high dielectric constant [45] and is thermodynamically stable next to silicon under equilibrium conditions, interfacial reactions occur which produce materials with lower k such as SiO<sub>2</sub> or silicate thereby seriously diminishing the total capacitance. Also, HfO<sub>2</sub> and ZrO<sub>2</sub> tend to crystallize at relatively low temperature, leading to the formation to poly-crystalline films, with enhanced leakage current paths along the grain boundaries [38, 45]. HfO<sub>2</sub> is an ionic conductor, as O ions can diffuse through the oxides and leave vacancies behind which can act as traps and reliability concerns [45]. So to prevent these shortcomings in the oxide dielectrics HfSi<sub>x</sub>O<sub>v</sub> is used. HfSi<sub>x</sub>O<sub>v</sub> is also stable in direct use with silicon, and by incorporating a sufficiently high level of Silicon during deposition, the dielectric-Si interface will act more like the preferable SiO<sub>2</sub>-Si interface, and the driving force is removed for any reaction between the substrate and the dielectric [46]. Use of HfSi<sub>x</sub>O<sub>v</sub> allows the control of silicon interface and also affords the significant flexibility for the use of poly-silicon gate [45]. Moreover HfSi<sub>x</sub>O<sub>v</sub> remains amorphous at temperatures greater than 900°C. So though HfSiO has a dielectric constant K=11 with 6% Hf, [38] they have some characteristics that are better than HfO<sub>2</sub> and hence can be used a gate dielectric. HfSi<sub>x</sub>O<sub>v</sub> dielectric materials have better leakage characteristics, improved threshold voltage characteristics, lower mobility degradation and allow larger thermal budgets during processing than HfO<sub>2</sub> [47]. Due to this reason we have chosen HfSi<sub>x</sub>O<sub>y</sub> as gate dielectric material in our process. HfSi<sub>x</sub>O<sub>y</sub> films (with smaller k compared to HfO<sub>2</sub> and phonon energy larger than HfO<sub>2</sub>) as gate insulator show mobility closer to the SiO<sub>2</sub> based devices. The HfSi<sub>x</sub>O<sub>y</sub> based devices may provide sufficient gate leakage

reduction at desired electrical oxide thickness without too much loss of carrier mobility [48].

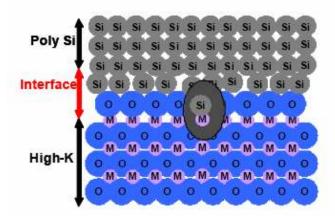

Though high-k dielectric materials look very promising, there are certain challenges that have to be met before successful transition from SiO<sub>2</sub> to high-k. Among them some are noteworthy. First problem is with replacing polySi/SiO<sub>2</sub> stack with polySi/high-k stack. Due Fermi level pinning at the polySi/high-k interface, high-k dielectrics and polySi are incompatible. The Fermi level pinning is most likely caused by defect formation at the polySi/high-k interface [29, 33, 49]. This causes high threshold voltages in high-k transistors.

Figure 1.14 Defect formation at the poly-Si and high-k dielectric interface [29]

Apart from the problem of high threshold voltage, presence of electrical instabilities of the threshold voltage in the electrical performance of high-k transistors is another problem which seriously comprises the performance and long term operation of the device. They cause hysteresis in the  $I_d$  Vs  $V_G$  characteristics when ramping the gate voltage up and down [33, 37]. Long term reliability and expected lifetime of the high-k

stacks are important issues. Issues like Stress induced leakage current (SILC) generation [33], time dependent dielectric breakdown (TDDB)[33, 37] and negative bias temperature instability (NBTI) [33, 37] are being investigated. But the most important issue with the high-k gate dielectric material is the mobility degradation. This is discussed in detail in the subsequent section.

### 1.5 Mobility Degradation in High-K Dielectric Materials

The most challenging problem for the high-k dielectrics in the present scenario is the transistor drive performance, which is directly linked to the carrier mobility in the channel [33]. Several factors can limit the inversion channel mobility in the transistors with high-k gate dielectric material. The scattering mechanisms like Coulomb scattering, soft phonon scattering and surface roughness scattering, and charge trapping contribute to the mobility degradation. Along with that, the thickness and material quality of the interfacial oxide layer can also influence the results [48]. It is found that high-k layers demonstrate lower mobility than conventional SiO<sub>2</sub>. The problem is more severe for n-channel than for p-channel devices [33]. The materials with largest k values show the poorest mobility because of the correlation between mode energy and amplitude and the k value [48].

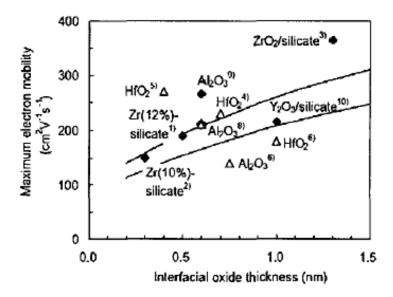

Coulomb scattering due to high density of interface trapped charges and fixed oxide charges appears to be an important contributor [50, 51]. It was observed that higher the interface trap density, lower the mobility. The interface trap density near the conduction band is higher than that near the valence band. Consequently degradation in hole mobility in p-MOS is less then electron mobility in n-MOS [52]. Coulomb

scattering dominates at low field regime [48]. The low mobility values in the high-k gate stacks as well as its dependence on interfacial oxide thickness can be explained by assuming that Coulomb potential is responsible for scattering of electrons [48]. The Fig. 1.15 demonstrates the reduction in maximum mobility with decreasing interfacial oxide thickness. The solid symbols denote metal gates and open symbols denote poly-Si gates [33].

Figure 1.15 Reduction in maximum mobility with decreasing thickness of interfacial oxide. [33]

The high-k dielectrics can suffer from severely degraded mobility due to the coupling of low energy surface optical phonons which arise from the polarization of the high-k dielectric to the inversion channel charge carriers [29, 31]. The scattering by phonons limits inversion layer electron mobility at the medium field regime and low lattice temperatures [48]. Mobility due to soft optical phonons in high-k was found to be significantly lower than its SiO<sub>2</sub> counterpart. This indicates severe phonon scattering for the former [52]. It was indicated that mobility degradation in high-k dielectric materials

is intrinsic and is related to scattering by soft phonons. Severe mobility degradation due to phonon scattering was reported in high-k/polySi stacks as compared to SiO<sub>2</sub>/polySi stacks [48, 53, 54].

The lower mobilities are also due to aggressive interfacial oxide thickness used for these stacks. The peak mobility in n-MOS devices with high-k layer is observed to increase along the thickness of the interfacial SiO<sub>2</sub> or SiON. This proves that the scattering mechanism that reduces the mobility becomes less important when the high-k is further away from the channel. So it is very vital to specify the thickness of the interfacial oxide when comparing values of mobilities from different gate stacks [33, 55].