# A THEORETICAL FRAMEWORK FOR DESIGN SPACE EXPLORATION OF MANYCORE PROCESSORS

by

# **HUN JUNG**

Presented to the Faculty of the Graduate School of

The University of Texas at Arlington in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT ARLINGTON

December 2011

Copyright © by Hun Jung 2011

All Rights Reserved

# **ACKNOWLEDGEMENTS**

First of all, I want to express my deepest appreciation to Dr. Hao Che. Without his careful guidance, encouraging advises, I would have been in trouble keeping my research going to its completion. His strong theoretical and practical knowledge of the network and system architectures have led me to obtain better solutions in various problems I have faced. I would also like to thank all the committee members: Dr. Roger Walker, Dr. Mohan Kumar, Dr. Ramez Elmasri for valuable advises on my research.

I also want to tell all my friends that I have enjoyed their personalities and supports. In particular, I am thankful for the enjoyable friendship and valuable discussions I have had with David Levine and Miao Ju throughout the years.

Finally, I'd like to express my deep appreciation for my parents' endless support and care. Last but not the least, I would like to thank my wife and my two princesses for their constant patience, love and support.

October 27, 2011

# **ABSTRACT**

# A THEORETICAL FRAMEWORK FOR DESIGN SPACE EXPLORATION OF MANYCORE PROCESSORS

# Hun Jung, PhD

# The University of Texas at Arlington, 2011

Supervising Professor: Hao Che

As design space and workload space in multicore era are continuously expanding, it is a challenge to identify optimal design points quickly during the early stage of multicore processor design or programming phase. To meet this challenge, a thread-level modeling methodology is developed in this dissertation. The idea is to model multicore processors at the thread-level, overlooking instruction-level and microarchitectural details. Since the thread-level modeling is much coarser than the instruction-level modeling, the analysis at this level turns out to be significantly faster than that at the instruction level. This feature makes the methodology particularly amenable to fast performance evaluation for manycore systems in a large design space.

Based on this methodology, we developed a thread-level simulation tool for quick evaluation of any given design point and also a theoretical framework that can capture the general performance properties for a class of multicore processors of interest over a large design space and workload space, free of scalability issues. In the theoretical framework, queuing network models that model multicore processors at the thread level are developed and

iν

scalability issues in the queuing networks are solved based on an iterative algorithm over a large design space and workload space. This framework scales to virtually unlimited numbers of cores and threads.

For the simulation tool, case studies based on a large number of code samples available in IXP1200/2400 workbenches show that the maximum throughput estimated using our tool are consistently within 6% of cycle-accurate simulation results. Moreover, each simulation run takes only a few seconds to finish on a Pentium 4 computer, which strongly demonstrates the power of this tool for fast communication processor (CP) performance testing. For the theoretical frame work, the testing results demonstrate that the throughput performance for manycore processors with 1000 cores can be evaluated within a few seconds on an Intel Pentium 4 computer and the results are within 5% of the simulation data obtained based on the thread-level simulator tool.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                       | iii  |

|--------------------------------------------------------|------|

| ABSTRACT                                               | iv   |

| LIST OF FIGURES                                        | viii |

| LIST OF TABLES                                         | ix   |

| Chapter                                                | Page |

| 1. INTRODUCTION                                        | 1    |

| 2. METHODOLOGY OF MODELING MULTICORE PROCESSORS        | 5    |

| 2.1 Thread-Level Modeling                              | 5    |

| 2.2 Design Space                                       | 8    |

| 3. SIMULATION TOOL                                     | 16   |

| 3.1 Design Idea                                        | 16   |

| 3.2 Simulation Architecture                            | 19   |

| 3.3 Sustainable Line Rate Estimation                   | 25   |

| 3.4 Simulation Testing                                 | 29   |

| 3.4.1 Simulation Setups                                | 29   |

| 3.4.2 Test Results                                     | 34   |

| 3.5 Related Work                                       | 36   |

| 4. THEORECTICAL FRAMEWORK FOR DESIGN SPACE EXPLORATION | 38   |

| 4.1 Queuing Network Model                              | 38   |

| 4.2 Iteration Algorithm                                | 41   |

| 4.3 Testing                                            | 44   |

| 4.3.1 Accuracy Test                                    | 44   |

| 4.3.2 Example of Design Space Exploration              | 49   |

| 4.4 Related Work         | 53 |

|--------------------------|----|

| 5. CONCLUSION            | 57 |

| APPENDIX                 |    |

| A. SAMPLE CODE PATHS     | 58 |

| REFERENCES               | 64 |

| BIOGRAPHICAL INFORMATION | 70 |

# LIST OF ILLUSTRATIONS

| Figure                                                                                   | Page |

|------------------------------------------------------------------------------------------|------|

| 1.1 Comparison of Our Approach with Function Analysis                                    | 3    |

| 2.1 An Example of Code Path                                                              | 5    |

| 2.2 Execution Sequence for Coarse-Grained Core                                           | 6    |

| 2.3 Queuing Network Models                                                               | 7    |

| 2.4 Design Space                                                                         | 9    |

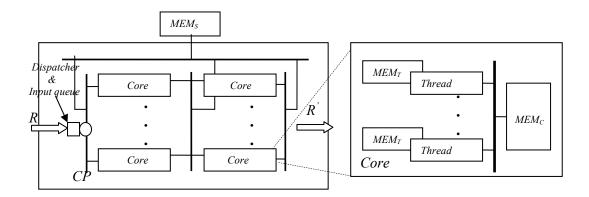

| 3.1 Generic CP Organization                                                              | 19   |

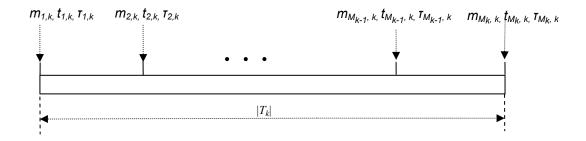

| 3.2 A graphical Representation of A Code Path                                            | 21   |

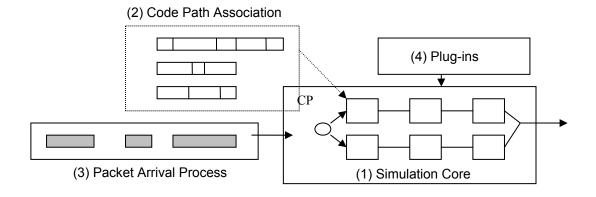

| 3.3 CP Simulation Model                                                                  | 23   |

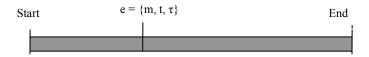

| 3.4 An Example of Event-Annotated Code Path                                              | 24   |

| 3.5 Event-Level Simulation                                                               | 25   |

| 3.6 Pipeline Configuration for Packet Count, Generic IP Forwarding and Layer-2 Filtering | 31   |

| 3.7 Pipeline Configuration for ATM/Ethernet Forwarding                                   | 31   |

| 3.8 Ingress Blocks for IXP2400 Code Samples                                              | 33   |

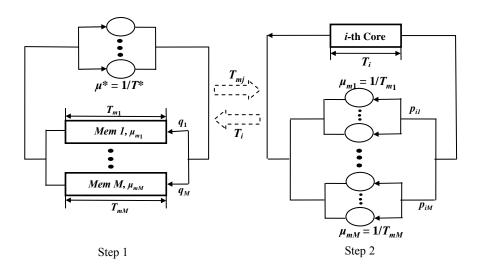

| 4.1 An Iterative Procedure for Decoupling Shared Memories                                | 43   |

| 4.2 Iteration Algorithm                                                                  | 44   |

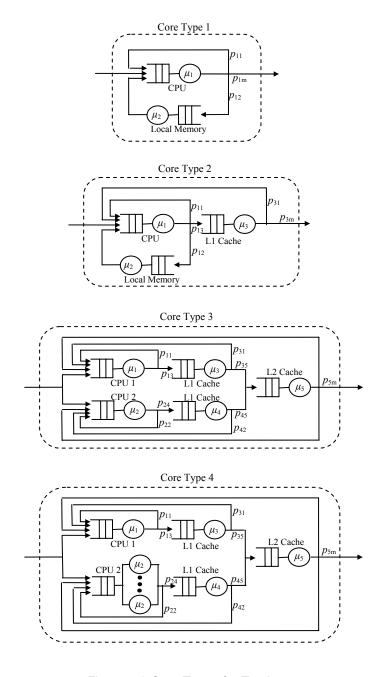

| 4.3 Core Types for Testing                                                               | 45   |

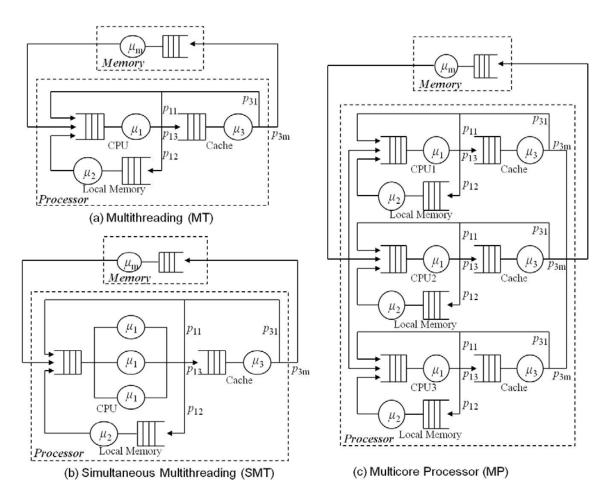

| 4.4 Processor Types                                                                      | 50   |

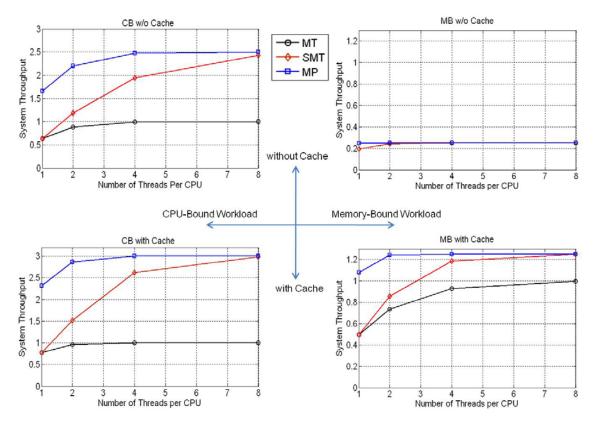

| 4.5 Throughputs in MT, SMT, and MP with Multidimensional Changes                         | 52   |

# LIST OF TABLES

| Table                                                                                             | Page |

|---------------------------------------------------------------------------------------------------|------|

| 2.1 Component Modeling Using Queuing Models with Local Balance Equations                          | 11   |

| 3.1 The Tool versus CAS (IXP1200) for Packet Counting                                             | 35   |

| 3.2 The Tool versus CAS (IXP1200) for Generic IPv4 Forwarding                                     | 35   |

| 3.3 The Tool versus CAS (IXP1200) for ATM/Ethernet IP Forwarding                                  | 35   |

| 3.4 The Tool versus CAS (IXP1200) for Layer-2 Filtering                                           | 36   |

| 3.5 The Tool versus CAS (IXP2400) with 8 Threads                                                  | 36   |

| 4.1 All and Each Type's Throughputs with Various Common Memory Service Time                       | 47   |

| 4.2 Changes in All Cores in Group 1 ( $\mu_1 = 0.05 \rightarrow 0.03$ , $m_1 = 6 \rightarrow 8$ ) | 48   |

| 4.3 A Change in One Target Core in Group 4 (L2 hit rate 98% -> 90%)                               | 48   |

#### CHAPTER 1

#### INTRODUCTION

As multicore processors (MPs) become the mainstream processor technology, challenges arise as to how to design and program MPs to achieve desired performance for applications of diverse nature. This type of processors is generally built based on either specially designed processor cores, as in the case of Communication Processors (CPs) [1], or general purpose processor cores [2]. There are two scalability barriers that the existing MP analysis approaches (e.g., simulation and benchmark testing) find difficult to overcome. The first barrier is the difficulty for the existing approaches to effectively analyze MP performance as the numbers of cores and threads of execution become large. The second barrier is the difficulty for the existing approaches to perform comprehensive comparative studies of different architectures as MPs proliferate. In addition to these barriers, how to analyze the performance of various possible design/programming choices during the initial MP design/programming phase is particularly challenging, when the actual instruction-level program is not available.

To overcome the above scalability barriers, approaches that work at much coarser granularities (e.g., overlooking microarchitectural details) than the existing approaches should be sought to keep up with the ever growing design space. Such an approach should be able to characterize the general performance properties for a wide variety of MP architectures and a large workload space at coarse granularity. Moreover, such an approach should not require the availability of the instruction-level programs as input for performance analysis. The aim is to narrow down the design space of interest at coarse granularity, in which the existing approaches can work efficiently to further pin down the optimal points at finer granularities. To

this end, we believe that an overarching *theoretical* approach, encompassing both existing and future design and workload spaces, must be sought. In this dissertation, we develop a simulation tool and a theoretical framework of such kind.

A common unique feature is employed in both our simulation tool and theoretical framework to overcome the scalability barriers. First, they works at the thread level, overlooking instruction-level and microarchitectural details, except those having significant impact on thread level performance. A simulation tool developed at this granularity [3] was found to be capable of predicting the system performance pretty accurately, i.e., within 6% of the cycle-accurate simulation results. Also, the theoretical framework testing [52] demonstrates that the throughput performance for many-core processors with 1000 cores can be evaluated within a few seconds on an Intel Pentium 4 computer and the results are within 5% of the simulation data obtained based on the simulation tool. The performance data within 5-6 % of actual performance in this programming phase should be considered reasonably accurate. This is because such performance data is obtained using a piece of pseudo code with normally inaccurate instruction count, not the executable program itself, as input. The program developed in later phases can generally be fine tuned to compensate for such loss of accuracy. Moreover, as we shall see in Chapter 3 and 4, this granularity is particularly amenable to large design space exploration in both simulation and theoretical analysis.

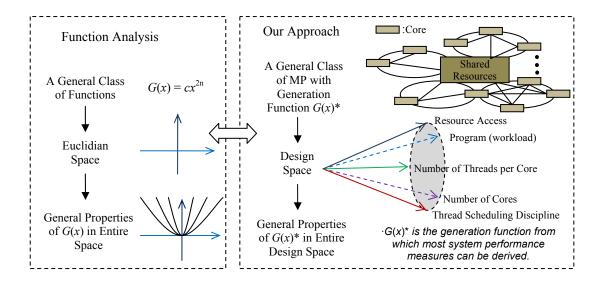

The unique feature in our theoretical framework is that the approach taken for the design space exploration is unconventional. Instead of exploring the design space based on sampled points in the space, the framework directly study the general performance properties of system classes over the entire design space. Here a system class characterizes a class of multicore architectures, a workload space, and a set of performance measures. Understanding the general performance properties of a system class leads to the understanding of the properties of all individual points in the design space (i.e., specific multicore architectures, specific workloads, and the associated performance data). This approach is quite similar to

Function Analysis in mathematics that analyzes general properties of functions over the entire vector space, as illustrated in Figure 1.1. At the core of this approach is to derive the generation function G(x) for a system class of interest defined in a large design space, through which all the performance measures can be further derived. In our framework, the design space and system classes are expressed mathematically using the language of queuing network models.

In this dissertation, we make the following major contributions. First, we develop a novel design methodology which is a thread-level modeling technique for multithreaded MPs. Second, based on this modeling technique, we build a simulation tool which is fast and generic. Third, we develop the theoretical framework that allows G(x) to be derived for classes of multicore processors with virtually unlimited numbers of cores, overcoming the above mentioned scalability barriers.

Figure 1.1 Comparison of Our Approach with Function Analysis

The rest of the dissertation is organized as follows. Chapter 2 describes the proposed methodology which is applied to both the simulation tool and the theoretical framework. Chapter 3 introduces the simulation tool. Chapter 4 shows how the theoretical framework is defined and developed. Finally, Chapter 5 concludes the dissertation.

### CHAPTER 2

# METHODOLOGY OF MODELING MULTICORE PROCESSORS

In this chapter, we first describe the thread-level modeling concepts and how the thread-level modeling can be mapped to queuing network models. Then we introduce a large design space that can be represented in terms of queuing network models, whose generation functions have closed-form solutions.

# 2.1 Thread-Level Modeling

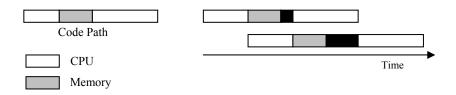

At the core of the simulation tool and theoretical framework is the modeling of the workload, defined as a mapping of program tasks to threads in different cores and system components, known as *code paths*. As shown in Figure 2.1, a code path handled by a given thread in a given core is a sequence of segments (measured in the unit of CPU cycles) representing the durations the thread is serviced by the CPU and other resources (not including queuing delays or other idle times) throughout the execution of the entire program or program task.

Figure 2.1 An Example of Code Path

The code path is defined at the thread level, in the sense that it only captures the events that have major impact on the thread-level performance. In other words, the instruction-level and microarchitectural details are overlooked, unless they trigger events that may have a significant effect at the thread level, such as an instruction for memory access that causes the thread to stall or instructions corresponding to a critical region that causes serialization effect at the thread level. A code path defined at this level can be easily derived from a pseudo code, rather than an instruction-level program, which may not be available during the processor design or initial programming phase.

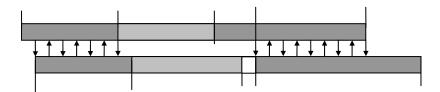

Correspondingly, all the components including CPU, cache/memory, and interconnection network are modeled at a highly abstract level, overlooking microarchitectural details, just enough to capture the thread-level activities. For example, for a CPU running a coarse-grained thread scheduling discipline and a FIFO memory, they are modeled simply as queuing servers running a coarse-grained thread scheduling algorithm and FIFO discipline, respectively. As an example, we consider a single coarse-grained core with a FIFO memory. The core runs two active threads loaded with the same code path (on the left in Figure 2.2). The execution sequence is shown on the right in Figure 2.2. The black segments are thread idle times for the CPU.

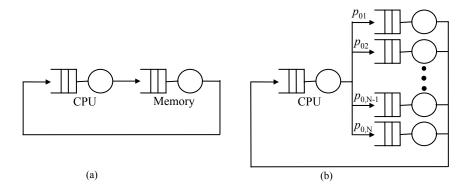

Now consider a closed queuing network composed of two FIFO queuing servers, modeling the coarse-grained CPU and the FIFO memory, as shown in Figure 2.3 (a). Assume that there are two jobs circulating in this network, modeling the two active threads.

Figure 2.2 Execution Sequence for Coarse-Grained Core

Figure 2.3 Queuing Network Models

As one can see, without considering the queuing times or thread waiting times, a thread making a round-trip, CPU-to-Memory-to-CPU, plus CPU-to-Memory, generates three segments corresponding to the code path in Figure 2.2. If the service times at the CPU and the memory exactly match the corresponding segment lengths of the code path, this queuing network model exactly emulates the execution sequence for that thread. Now, with two threads, it is not difficult to convince ourselves that due to the queuing effect, the two threads making such a trip will generate the same pattern of the execution sequence as the one on the right in Figure 2.2. Again, if the service times exactly match the segment lengths, the thread circulation exactly recovers the execution sequence in Figure 2.2.

So far we have been trying to emulate the actual execution process for the threads, which is no different from simulating the actual process at the thread level. Now we need to realize that the queuing models are in essence stochastic models, which are meant to capture long-run stochastic/statistic effects of a real system (open queuing network models may need to be used if the workload may be on and off, which however, can always be transformed into closed queuing network models [4]). In other words, the service time for a queuing server is in general a random number, following a given distribution, denoted as  $\mu_i$ , for queuing server i. As a result, it is the distribution of the segment lengths, not the individual segment lengths, that

needs to be used to characterize the service time. Moreover, for a code path that characterizes a workload for a processor with multiple parallel resources, such as the one in Figure 2.1, the corresponding closed queuing network, as depicted in Figure 2.3 (b), also involves a routing probability  $p_{0i}$  for a thread to go to the *i*-th resource upon exiting the CPU server. This parameter should also be evaluated statistically by counting the frequency of such occurrences in the long-run code paths handled by these threads.

From the above examples, we conclude that at the thread level, any types of MPs with N components and any long-run workloads can be generally modeled as a closed queuing network with N queuing servers of various service types in terms of queue scheduling disciplines and a workload space ( $\{\mu_i\}$ ,  $\{p_{ij}\}$ ) spanned by various possible combinations of service time distributions and routing probabilities. The central task of this framework is to develop mathematical techniques to analytically solve this closed queuing network model. The solution should be able to account for as many service types and as large a workload space as possible, aiming at covering a large design space.

Finally, with regard to the workload, there is a fundamental difference between analytical modeling and simulation/benchmark testing. For the latter, one does not know the actual code path until the testing is over (since there might be conditional branching and dynamic program generation at runtime), whereas for the former, one can assume that the actual code path is known in advance (since the aim of analytic modeling is to try to explain what have happened, i.e., answering "what causes what" and "what if" types of questions).

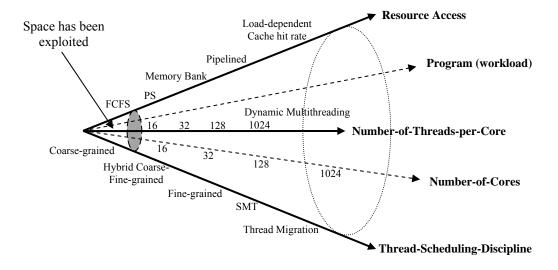

## 2.2 Design Space

We want the design space to be as large as possible to encompass as many multicore architectures and workloads as possible. Figure 2.4 depicts such a design space. It is a five dimensional space, including resource-access dimension, thread-scheduling-discipline dimension, program dimension, number-of-thread-per-core dimension, and number-of-core dimension.

Figure 2.4 Design Space

The Thread-Scheduling-Discipline dimension determines what CPU or core type is in use. The existing commercial processors use fine-grained, coarse-grained, simultaneous multithreading (SMT), and hybrid coarse-and-fine-grained thread scheduling disciplines. Some systems may also allow a thread to be migrated from one core to another.

The Resource-Access dimension determines the thread access mechanisms to MP resources other than CPU. It may include memory, cache, interconnection network, and even a critical region. The typical resource access mechanisms include first-come-first-serve (FCFS), process sharing (parallel access), parallel resources (e.g., memory bank), and pipelined access. For cache access, a cache hit model may have to be incorporated, which may be load dependent.

The Program dimension includes all possible programs. This dimension is mapped to a workload space, involving all possible code paths, for a given type of processor organization (e.g., a code path for a single-core processor with three parallel resources as in Figure 2).

We expect that both Number-of-Cores and Number-of-Threads-per-Core dimensions will reach thousands in the near future. Our theoretical framework needs to be able to deal with MPs of such scale. Moreover, the theoretical framework needs to be able to account for dynamic multithreading, where the number of threads used for a program/program task may change over time.

The queuing network modeling techniques at our disposal restrict the size of the design space to one that must be mathematically tractable. This makes the coverage of the design space in Figure 2.4 a challenge. As shown in Figure 2.4 (i.e., the small cone on the left), the part of the design space that has been (incompletely) explored by the existing work using queuing network modeling techniques is only a tiny part of the entire space.

In what follows, we discuss how our framework allows almost the entire design space in Figure 2.4 to be explored, except dynamic multithreading. We look at different dimensions of the design space separately.

Resource-Access and Thread-Scheduling-Discipline Dimensions: Without resorting to any approximation techniques, the existing queuing network modeling techniques will allow both of these dimensions to be largely explored analytically. Any instance in either of these two dimensions can be approximately modeled using a queuing server model that has local balance equations (i.e., it leads to queuing network solutions of product form or closed form). More specifically, Table 2.1 shows how individual instances in these two dimensions can be modeled by three queuing models with local balance equations, including M/G/∞; M/M/m FCFS (including M/M/1); and M/G/1 PS (Processor Sharing).

Note that the memory banks should be modeled as separate queuing servers and hence, are not listed in this table. Also note that for all the multithread scheduling disciplines except the Hybrid-Fine-and-Coarse-Grained one (to be explained below) in Table 2.1, the service time distribution of a queuing model models the time distribution for a thread to be

serviced at the corresponding queuing server. With these in mind, the following explains the rationales behind the mappings in Table 2.1:

Table 2.1 Component Modeling Using Queuing Models with Local Balance Equations

| Queue Model Component                                                        | M/G/∞     | M/M/m<br>FCFS | M/G/1 PS  | M/M/1    |

|------------------------------------------------------------------------------|-----------|---------------|-----------|----------|

| SMT                                                                          | $\sqrt{}$ | $\checkmark$  |           |          |

| Fine-Grained Thread scheduling                                               |           |               | $\sqrt{}$ |          |

| Coarse-Grained Thread scheduling                                             |           |               |           | <b>√</b> |

| Hybrid-Fine-and-Coarse-Grained Thread scheduling                             |           | V             |           |          |

| Resources dedicated to individual threads                                    | V         |               |           |          |

| FCFS shared Memory, Cache,<br>Interconnection Network, or<br>Critical Region |           |               |           | <b>√</b> |

| FCFS Memory with Pipelined Access                                            |           | V             |           |          |

- SMT: It allows multiple issues in one clock cycle from independent threads, creating multiple virtual CPUs. If the number of threads in use is no greater than the number of issues in one clock cycle, the CPU can be approximately modeled as an M/G/∞ queue, mimicking multiple CPUs handling all the threads in parallel, otherwise, it can be modeled as an M/M/m queue, i.e., not enough virtual CPUs to handle all the threads and some may have to be queued.

- Fine-grained thread scheduling discipline: All the threads access the CPU resource will share the CPU resource at the finest granularity, i.e., one instruction per thread in a round-robin fashion. This discipline can be modeled as an M/G/1 PS queue, i.e., all the threads share equal amount of the total CPU resource in parallel.

- Coarse-Grained thread scheduling discipline: All the threads access the CPU resource

will be serviced in a round-robin fashion and the context is switched only when the

thread is stalled, waiting for the return of other resource accesses. This can be

approximately modeled as a FCFS queue, e.g., an M/M/1 queue.

- Hybrid-Fine-and-Coarse-Grained thread scheduling discipline: It allows up to a given number of threads, say m, to be processed in a fine-grained fashion and the rest be queued in a FCFS queue. This can be modeled as an M/M/m FCFS queue. In this queuing model, the average service time for each thread being serviced is m times longer than the service time if only one thread were being serviced, mimicking finegrained processor sharing effect.

- Resources dedicated to individual threads: Such resources can be collectively modeled

as a single M/G/∞ queue, i.e., there is no contention among different threads accessing

these resources.

- FCFS Shared Memory, Cache, Interconnect Network, or Critical Region: This kind of resources can be approximately modeled as an M/M/1 queue.

- FCFS Memory with Pipelined Access: It can be modeled as an M/M/m FCFS queue.

The pipeline depth determines how many threads can be serviced simultaneous in the M/M/m FCFS queue.

We note that the resource access dimension also includes load-dependent cache hit rate. The cache hit probability (i.e., the routing probability to move back to the CPU) is generally load-dependent in the sense that it may be either positively or negatively correlated with the number of threads in use due to temporal locality or cache resource contention, respectively. These effects can be accounted for in our framework without approximation, by means of the existing load-dependent routing techniques (e.g. [5]).

We also note that the thread-scheduling-discipline dimension includes thread migration. The thread migration allows a thread to be migrated from one core to another for, e.g., load balancing purpose. This effect can be accounted for without approximation by allowing jobs to have non-zero probabilities to switch from one class to another [4] [6].

More capabilities may be identified and included in these two dimensions as long as they are mathematically tractable.

Program Dimension: In principle, this dimension can be fully explored through a thorough study of the workload space, characterized by the service time distributions and routing probabilities, i.e., a collection of  $(\{\mu_i\}, \{p_{ij}\})$ 's. However, for the solvable queuing server models in Table 2.1, such as M/M/m and M/M/1 queues, the service time distribution  $\mu_i$  is a given, i.e., exponential distribution. Since the exponential distribution is characterized by only a single parameter, i.e., the mean service time  $t_i$ , it can only capture the first order statistics of the code path segments corresponding to that server, hence providing a first order approximation of the program dimension or workload space. Although as part of our future work, we will consider more sophisticated queuing models in an attempt to overcome this limitation, it is widely recognized that the queuing performance for closed queuing networks is insensitive to the service distributions of the queuing servers, generally known as the property of robustness of the closed queuing networks [6]. Hence, we should expect that our first order approximation provides a good coverage of the workload space.

Number-of-Cores and Number-of-Threads-per-Core Dimensions: First, we note that the number of threads dimension should allow dynamic multithreading, meaning that at different program execution stages, the number of active threads may vary. We plan to use a set of ancillary thread classes with different delay loops to join and leave the queuing network modeling a core. It can be easily shown that with n job (or thread) classes and  $2^{i-1}$  threads in the i-th class for i = 1, ..., n, any number of threads in the range  $[1, 2^{n+1}-1]$  can be generated in the core. For example, with n = 4, any number of threads in the range of [1, 31] can be

generated. The first thread class has only one thread in it. This thread class runs in the queuing network modeling the core. The rest (n-1) thread classes run in the delay loops, It can also be shown that by properly setting the delay value for each delay loop, the proposed model can match any distribution of parallelism (i.e., with probability  $p_k$  that k threads are presented in the core). The queuing network with these delay loops has closed-form solution. Second, we need to address the scalability issues in calculating the generation functions as the numbers of cores and threads increase. We consider a general closed queuing network modeling an N-core (or core cluster) system with K shared resources. We want to be able to get closed-form generation function G for such closed queuing networks, from which any performance measures can be derived. As long as all the queuing servers in the system have local balance equations (e.g., following the queuing server models in Table 2.1), the generation function (also known as the normalization function in queuing theory) can be generally written as:

$$G = \sum_{\substack{\sum_{i=1}^{N+K} m_{i,1} = M_1 \\ \sum_{i=1}^{N+K} m_{i,N} = M_N}} \dots \sum_{\substack{j=1 \\ j=1}}^{N} f_j(m_{jj}) \prod_{j=N+1}^{N+K} f_j(m_{j1}, \dots, m_{jN})$$

(2.1)

where  $f_i(m_{ik})$  is a function corresponding to the probability that there are  $m_{ik}$  threads currently in core i (for i = 1,..., N) for thread class k (for k = 1,..., N, i.e., the threads from each core forms a class),  $f_j(m_{j1},...,m_{jN})$  is a function corresponding to the probability that there are  $m_{j1}$  threads of class one,  $m_{j2}$  threads of class two, and so on, in shared memory queuing server j (for j = N+1, ..., N+K), and  $M_i$  is the total number of threads belonging to core i (for i = 1,..., N).  $f_i$  takes different forms for different core organizations, in terms of e.g., CPU, cache, and local memory of different types from the resource-access dimension and thread-scheduling-discipline dimension of the design space.

On one hand, we note that G is defined in the entire design space (with the first order approximation of the program-dimension or workload space). Understanding the general

properties of G over this space will allow the properties of individual points in the design space to be understood, just like function analysis (see Figure 1.1). On the other hand, we also note that the number-of-core and number-of-thread-per-core dimensions create scalability barriers that prevent us from being able to effectively calculate G. This is because the computational complexity for G is O ( $N_S M^{N+K}$ ), where M is the average number of threads per core and  $N_S$  is the number of queuing servers per core. Our experiments on an Intel Core-Duo, T2400, 1.83 GHz processor showed that for  $N_S = M = 2$  and K = 1, it takes about 24 hours to compute the generation function for a 20-core system. Clearly, it is computationally too expensive to cover the entire number-of-core and number-of-thread dimensions. In chapter 4, we develop an iterative procedure to overcome this scalability barrier.

# CHAPTER 3

# SIMULATION TOOL

In this chapter, we describe our simulation tool for multicore processors based on the thread-level methodology introduced in Chapter 2. In particular, we focus on the simulation model for communication processors (CP), which is the most complex processors in the multicore processor family. The tool applies to other multicore processors as well. Our major goal is to focus on modeling features common to a wide variety of CP architectures and incorporate relevant CP specific features as plug-ins. This tool not only allows user-defined packet arrival processes and code path mixtures to be tested, but also provides a way to allow the maximum sustainable line rate to be quickly estimated. In Section 3.4, Case studies based on a large number of code samples available in IXP1200/2400 workbenches show that the maximum sustainable line rates estimated using our tool are consistently within 6% of cycle-accurate simulation results. Moreover, each simulation run takes only a few seconds to finish on a Pentium 4 computer, which strongly demonstrates the power of this tool for fast CP performance testing.

# 3.1 Design Ideas

The following three key ideas underlay the CP simulation tool development.

Focus on emulating common CP features while taking the relevant performance impacts of CP-specific features into account through user provided models. Our approach attempts to strike a balance between complexity and simplicity by adopting a hybrid simulation-and-modeling based approach. Specifically, our approach focuses on faithfully emulating important features common to a wide variety of CP architectures (e.g., multithreading and multi-

core) and account for the relevant performance impacts of CP-specific features (e.g., I/O interface, cache, memory, memory controller, and bus architectures) through user provided models, called plug-ins. For example, by focusing on the throughput, delay, and loss performance, our tool only requires a plug-in that captures the memory access latency for each CP memory. In other words, the plug-in only needs to capture the delay performance aspect of memory accesses, which can be modeled by the user, based on, for example, a queuing model or even an empirical chart, without having to emulate the processing details cycle-by-cycle. This design approach makes the simulation tool generic and adaptable to a wide range of CP architectures with the addition of a set of user provided plug-ins, capturing CP architecture specific features. With limited number of I/O and memory interfaces for CPs in general, the number of plug-ins needed are generally small, e.g., less than a dozen.

Capture important events only. The existing approach which attempts to accurately pin down the CP performance generally resorts to cycle-by-cycle or instruction-level simulation. This not only makes the simulation slow and storage space demanding, but also requires the availability of the executable program as input for the simulation. What is available to us, however, is only a piece of pseudo code for packet processing tasks mapped to each core, which defies the use of cycle-by-cycle simulation. Instead, we adopt the thread-level performance analysis methodology introduced in Chapter 2. Namely, we propose to identify a sequence of events that may have significant impact on the thread-level performance, identifiable from the pseudo code and perform event-by-event, rather than instruction-by-instruction simulation. Since the number of important events identifiable in each code path is generally small, e.g., one dozen to a few dozen, one can expect that event-by-event simulation would be significantly faster than cycle-by-cycle simulation. Identifying important events is not difficult. For throughput, delay, and loss performance analysis, the important events may include memory and I/O accesses that results in a context switching, cache accesses that may cause a context switching, events that cause serialization effects, such as a critical section, and events

that cause run-time code generation, such as packet fragmentation for which the code size is a function of the packet size. Although the instruction level activities, such as per instruction cycle time and instruction-level-pipelining (ILP) aborts, cannot be directly captured based on a piece of pseudo code, the average impact of these activities on the overall throughput, delay, and loss performance may be modeled. For example, by defining an event for code branching and associating with each branching event an average ILP abort cost in terms of wasted cycles, the impact of ILP aborts can be accounted for on average. In fact, using average data to simplify the simulation is not original. For example, the average per instruction cycle time has been widely used in processor performance analysis.

In summary, combining the event-by-event simulation and the separation of CP common features from CP specific features makes the tool very lightweight in terms of both time and space complexities. Moreover, simulation at the event level makes it possible to allow the use of pseudo code, rather than an exact program, as input for the simulation.

Allow for sustainable line rate estimation. No matter how lightweight a simulation tool would be, the simulation time is guaranteed to be prohibitively long if the goal is to perform exhaustive statistic analysis. This is because there are virtually unlimited numbers of possible packet arrival processes and mixtures of code paths the threads in each core may concurrently handle, which has made a CP the most difficult one to simulate, among all MPs in the MP family. Unless a user has in mind small numbers of targeted packet arrival processes and code path mixtures to be tested, performing exhaustive statistical analysis in a large design space is guaranteed to be extremely time consuming, if possible. In practice, for most CP programmers and designers, what they really want to know is, for a given task-to-CP-topology mapping, whether the CP can sustain wire-speed forwarding performance or not. Unfortunately, traditionally, the data inputs, including packet arrival processes and code path mixtures, are provided by the user of the tool, rather than part of the tool design. As a result, all the existing CP simulation tools were developed without being concerned with how the input data should be

generated. This makes it difficult for a user or designer to effectively use such a tool to test whether the CP can keep up with the line rate or not. To address this issue, as part of the tool design, we develop a systematic approach to allow the sustainable line rate to be estimated for any given task-to-CP-topology mapping. In this approach, the user does not have to provide any packet arrival processes, nor code mixtures as input to the tool, but simply a piece of pseudo code for the tasks mapped to each core. The tool will automatically return the line rate the CP can sustain, under such a mapping.

# 3.2 Simulation Architecture

In this Section, we introduce the generic CP organization, the code path definition, the simulation model, and an approach to estimate the sustainable line rate.

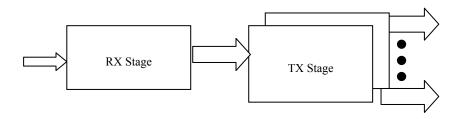

Figure 3.1 Generic CP Organization

Generic CP Organization: Based on the aforementioned methodology, we consider a generic CP organization depicted in Figure 3.1. This organization focuses on the characterization of multicore and multithreading features common to most of the CP architectures, leaving all other components being summarized in highly abstract forms. More specifically, in this organization, a CP is viewed generically as composed of a set of cores and a set of on-chip or off-chip supporting components, such as I/O interfaces, memory, level one and

level two caches, special processing units, scratch pads, embedded CPUs, and coprocessors. These supporting components may appear at three different levels, i.e., the thread, core, and system (including core cluster) levels, collectively denoted as  $MEM_T$ ,  $MEM_C$ , and  $MEM_S$ , respectively. Each core supports multiple threads which are scheduled based on a given thread scheduling discipline. Cores may be configured in parallel and/or multi-stage pipeline (a two-stage configuration is shown in Figure 3.1). Packet processing tasks are partitioned and mapped to different cores at different pipeline stages or different cores at a given stage. A dispatcher distributes the incoming packets to different core pipelines based on any given policies. Backlogged packets are temporarily stored in an input buffer. A small buffer may also present between any two consecutive pipeline stages to hold backlogged packets temporarily. Packet loss may occur when any of these buffers overflow. The tool is concerned with the CP throughput, latency, and loss performance only and the power and memory resource constraints are assumed to be met. This implies that we do not have to keep track of memory or program store resource availabilities or power budgets.

Code Path: The code path concept was introduced in Chapter 2. Here we give a more accurate definition of it. A code path is defined at the core level. For tasks mapped to a given core, a piece of pseudo code for these tasks can be written. Then a unique branch from the root to a given leaf in the pseudo code is defined as a code path associated with that core. An incoming packet to the core is accepted if there is a free thread in the core, and is associated with one code path, or a sequence of instructions that the core needs to execute throughout the life-time that the packet is in that core.

In this simulation model, a code path is broken down into a sequence of segments of instructions intermediated by events. For each segment, we are only concerned with the segment length, i.e., the number of instructions in the segment (which can be easily estimated on the basis of the pseudo code), or more precisely, the number of core cycles the core

arithmetic logical unit (ALU) has to spend on the segment, assuming the average per instruction cycle time is known. Hence, a code path can be formally defined as follows:

$T_k(M_k; m_{1,k}, t_{1,k}, \tau_{1,k}, \ldots, m_{Mk, k}, t_{Mk, k}, \tau_{Mk, k})$ : Code path k with event  $m_{i,k}$  occurred at the  $t_{i,k}$ -th core clock cycle and with event duration  $\tau_{i,k}$ , where  $k = 1, \ldots, K$  and  $i = 1, 2, \ldots, M_k$ , where K is the total number of code paths in the pseudo code mapped to the core and  $M_k$  is the total number of events in the code path.

$|T_k|$ : the code path length or the total number of core clock cycles in the code path  $T_k(M_k; m_{1,k}, t_{1,k}, \dots, m_{Mk, k}, t_{Mk, k}, \tau_{Mk, k})$ , where  $k = 1, 2, \dots, K$ .

A graphical representation of such a code path is given in Figure 3.2.

Figure 3.2 A graphical Representation of A Code Path

We note that a code path thus defined is simply a sequence of events with event interarrival times  $(t_{i+1,k} - t_{i,k})$  for  $i = 1, 2, ..., M_k - 1$ . We also note that the first instruction and the last instruction in the code path must be treated as events. For these events,  $\tau_{i,k} = 0$ . For an event  $m_{i,k} \in MEM_T$ ,  $MEM_C$ , or  $MEM_S$ ,  $\tau_{i,k}$  represents the loaded resource access latency. To account for the serialization effect caused by, for example, a critical section, two events must be included, indicating the start and end of the critical section. Again, for these events,  $\tau_{i,k} = 0$ .

An important event is defined as one that is expected to have an impact on the throughput, delay, and loss performance. Currently, we have defined the following four types of important events: (1) events for the start and end of the code path; (2) resource access events

which may cause significant delay and thread level interactions (context switching), events  $m_{i,k} \in MEM_T$ ,  $MEM_C$ , or  $MEM_S$ ; (3) events that cause a serialization effect; and (4) events that cause dynamic code generation. More types of events can be incorporated if they are expected to contribute significantly to the throughput, delay, and loss performance. For example, a new type of event that identifies branching points in the code can be included for the purpose of estimation of ILP abort cost caused by branching, if the abort effect cannot be neglected.

Simulation Model: Our simulation tool focuses on three performance measures: throughput, delay, and loss. All three measures can be obtained at runtime as long as the latency  $L_k$ , a packet with code path k in each core can be simulated, which can be expressed conceptually as:

$$L_k = |T_k| + \sum_{j=1:Mk} (\tau_{j,k} + \tau_{j,k}^W), \tag{3.1}$$

where  $r_{j,k}^w$  is the thread waiting time in the ready state after the event  $m_{j,k}$  finishes and  $r_{j,k}^w = 0$  if event  $m_{j,k}$  does not cause a context switching. For  $m_{i,k} \in MEM_T$ ,  $MEM_C$ , or  $MEM_S$ ,  $r_{j,k}$  is dependent on the nature of  $m_{j,k}$  access (number of memory reads or writes), the access speed (bus speed and memory speed), and access contention resolution mechanisms, such as the memory access pipelining and queuing architectures, which must be estimated based on a user provided plug-in.  $r_{j,k}^w$  is dominated by multithreading effects, which is the core parameter to be simulated at runtime.  $|T_k|$  is the total number of core clock cycles the core ALU spends on the packet.

Hence, for throughput, delay, and loss performance analysis, in general, all we need from the user is a set of plug-ins that estimate  $\tau_{j,k}$  for  $m_{i,k} \in MEM_T$ ,  $MEM_C$ , or  $MEM_S$  at runtime. Note that, although modeling CP-specific features in general is a nontrivial task, it should not be difficult to come up with empirical memory access latency models, e.g., in the form of charts or tables for a given CP. For example, by loading a given memory with different number and types

of requests and measuring the corresponding loaded latencies using a cycle-accurate simulator or test board, one can build empirical charts or tables offline to be used to quickly estimate the memory access latency at runtime. There is no need to emulate the microscopic process for memory access at run-time, saving significant simulation time. As we shall see in the next section, with the unloaded memory access latencies provided by Intel, as well as a memory access waiting time estimated based on a simple FIFO queuing model, our simulation tool accurately characterizes IXP1200/2400 performance without further information about IXP1200/2400 specific features.

With the previously described preparation, now we describe our simulation model, which focuses on emulating non-CP specific components, including core topology, multithreading, code path, code path mixtures, and packet arrival processes, pertaining to all the CP architectures, with a limited number of plug-ins for resource access latency estimation. These plug-ins are pre-developed and plugged into the simulation model. Figure 3.3 gives a logic diagram for the proposed simulation model, which is composed of four major components: (1) a simulation core based on the generic CP organization described in Figure 3.1; (2) code path association with a packet in a core; (3) a packet arrival process; and (4) a set of plug-ins to the simulation core.

Figure 3.3 CP Simulation Model

Based on the generic CP architecture in Figure 3.1, the simulation model focuses on emulating multithreaded cores which can be configured in any pipeline/parallel topology. Each core is modeled at a highly abstract level, running any number of threads based on a given thread scheduling discipline (our current design includes fine-grained, coarse-grained, and TDM-based disciplines). No further details of the core are modeled. A thread in a core that receives a packet will be assigned a code path. The way to assign code paths to threads in a core determines the mixture of code paths in that core. The packet arrival process can be generated from real traces (which also determine the code path mixture in each core), stochastic models, or deterministic models. Traditionally, the code path assignment and packet arrival process generation are not part of the simulation tool design, but as user provided inputs. Since all four components can be designed independent of one another, the design of components (1) and (4) combined constitutes a fast performance analysis tool in the traditional sense. In other words, as in traditional approaches, our tool allows any user provided packet arrival processes and/or mixtures of code paths to be simulated. Our goal, however, is to also design components (2) and (3) (to be discussed in Section 3.3) such that for any given task-to-CP-topology mapping, the tool can quickly return the maximum line rate the CP can sustain.

With the CP organization in Figure 3.1 and the event annotated code path in Figure 3.2, the fast simulation tool is developed based on the event-driven simulation approach. To help understand why such a tool can be made to execute quickly, here we give an intuitive explanation by way of a simple example. Consider a code path in Figure 3.4.

Figure 3.4 An Example of Event-Annotated Code Path

In this code path, there are only three events, the start, end, and e. Event e takes place at the t-th cycle for resource, m, access with loaded latency r. Now consider two threads in a core, each handling a code path as in Figure 3.4. They share the ALU resource based on a finegrained thread scheduling discipline (i.e., switch context at every instruction). Figure 3.5 gives the instruction execution timeline for the two code paths. The dark gray parts represent the code path segments. The light gray parts represent the cycles spent on event e, i.e., the loaded m access latencies. The white part stands for the cycles spent in the ready state waiting for execution after event e finishes. In this case, each code path involves three event boundaries: the start of the code path, the end of the code path, and the start and end of event e. The arrows represent the switches of control from one thread to the other after executing one instruction. The idea is not to simulate each and every switch of control, but only the cycles at the event boundaries, i.e., the positions indicated by vertical lines. Since each code path may have up to a few dozens of events, only a few dozens of event boundaries need to be simulated per packet. As a result, the event-driven simulation tool that captures only those events can run several orders of magnitude faster than cycle-accurate simulation tools, as our testing results showed (a few seconds per simulation run on a Pentium 4 Computer).

Figure 3.5 Event-Level Simulation

### 3.3 Sustainable Line Rate Estimation

The simulation model proposed in the previous section allows any packet arrival processes and code path mixtures to be simulated. In this section, we go one step further by designing the packet arrival processes and the code path mixtures to allow the maximum line rate a CP can sustain to be quickly simulated.

In the router industry, the performance of a router is judged mainly by whether its network interface cards can sustain wire-speed forwarding performance or not. A typical testing scenario is to use back-to-back, minimum-sized packets running at the line rate as input for the testing and all the packets are loaded with a typical code path, such as the code path that carries out basic tasks for IP forwarding. Following this industry practice, we would have already achieved our objective. However, while the packet arrival process thus generated makes sense, the use of a "typical" code path to determine whether a CP can sustain wirespeed forwarding performance may not always be a good idea, as long as untypical code paths may occur with non-negligible probabilities. For this reason, we adopt the industry practice on packet arrival process, but design our own code path assignment mechanism. In what follows, we discuss these two aspects separately.

Packet Arrival Process: Denote R as the line rate. Then the minimum packet time is P/R, where P is the size of a minimum-sized packet. We define a deterministic packet arrival process as minimum-sized packet arriving at fixed packet time interval  $T_P$ . For this process, the packet arrival rate  $r = P/T_P$ . The r value at which the packet loss is about to occur is then the maximum line rate the CP can sustain and if  $r \le R$ , we say that the line rate R can be sustained. Here, what code path mixture should be used as input to the simulation is yet to be specified, discussed below.

Code Path Assignment: Assume the user of the tool does not have a typical code path mixture in mind to test whether the line rate can be sustained. Our goal is then to identify the worst-case mixture of code paths that gives the lowest line rate the CP can sustain. This will ensure that the estimated sustainable line rate can always be achieved, under any mixtures of code paths. To this end, we first make the following two important observations.

First, intuitively, it is clear that the worst-case scenario for a given core will occur only when all the code paths in a code path mixture are the same. This is because having one code path for all the threads in the core will stress a particular resource the most. For example, if the

longest code path may potentially create a bottleneck for the core ALU resource, then loading the core with this code path for all the threads will stress the core ALU resource the most. This observation significantly reduces the complexity for the identification of the worst-case mixture of code paths. In this case, one may then test different potential worst-case code paths separately, rather than different combinations of code paths, significantly reducing the number of test cases.

Second, with a deterministic arrival process and code path mixture, and at the saturated arrival rate, queuing cannot help improve the throughput performance simply because there is no traffic fluctuation to provide rooms for the buffers between pipeline stages to offload the queued packets once the queue levels build up. In this case, we may view a core pipeline as a buffer-free system and the throughput for a core pipeline is determined by the throughput at the bottleneck pipeline stage.

Based on these observations, we can logically decompose the problem into two sub-problems: (1) identifying the bottleneck pipeline stage; and (2) finding the worst-case code path that leads to the minimum throughput for the core at the bottleneck stage. In practice, these two sub-problems may not be separable. In what follows, we present a mechanism to address these problems.

In principle, the worst-case code path for one core must be associated with some given mixtures of code paths (not necessarily the worst-case mixtures of code paths) for other cores. The reason is that packet processing processes in different cores are coupled together through the sharing of supporting components of type  $MEM_S$  (see Figure 3.1). As a result, to identify the worst-case code path for a particular core, one must also identify the associated code path mixtures for other cores. These code path mixtures are then associated with the arriving packets as input to various cores that simulates the entire system (see Figure 3.1) as a whole. This simulation run will return the sustainable line rate for that core and this process must be repeated for all the cores to identify the bottleneck core. However, in practice, this coupling

effect is not strong for the following reasons. First, different cores in different pipeline stages generally carry out distinct packet processing tasks. For example, in a three stage pipeline, the first stage may perform initial processing of incoming packets by loading the packets into an external DRAM. The second stage may perform major packet processing functions, which may involve significant table lookups in an external SDRAM. The last stage may mainly provide queue scheduling functions. As a result, the chances for different stages to interact with one another through *MEM*<sub>S</sub> types of resource accesses are small. Second, due to the wide use of multiple external memory interfaces, memory banks, and core clusters sharing different L2 caches in CP design, such coupling effects are further reduced. Hence, in our current tool design, we simply overlook such coupling effects. Nevertheless, our tool can be easily extended to take such effects into account, e.g., by modeling the *MEM*<sub>S</sub> accesses from other cores as a background random process derived from the *core*-access-intensive code path loaded to other cores.

Without considering the inter-core coupling effects, the problem is then reduced to one of finding the worst-case code paths for individual cores, separately. The worst-case code path k by definition generates the largest core latency  $L_k$  (see Eq. (3.1)). However, since without simulation, we have no idea about the values for the last term in  $L_k$ . The approach taken is to simply neglect  $r^w_{j,k}$  and approximate  $L_k$  by  $|T_k| + \sum_{j=1:Mk} \tau_{j,k}$ , where  $\tau_{j,k}$  is now the unloaded latency. This approximate latency can be estimated easily for each and every code path. We simply select an x % of the code paths with the largest  $L_k$  values to be considered as potential worst-case code paths to be tested. The reason to choose x % rather than just the one with the largest approximated  $L_k$  to be tested is simply to compensate for the inaccuracy of such estimations.

An initial testing of the above approach is encouraging. We tested the above approach against 50 randomly generated pseudo codes with each having 100 to 1000 branches or code paths with multiple  $MEM_T$ ,  $MEM_C$ , and  $MEM_S$  types of memory accesses. Since the tool finishes

running each case within 10 seconds on a Pentium IV PC, an exhaustive search of the worst-case code path for each pseudo code was performed. The worst-case code path thus found is then compared against the ones found by the above approach. For all 50 cases, we find that the true worst-case code path always falls into the top 1% (i.e., x = 1) of the entire code paths pool. This means that even for a pseudo code with up to 1000 code paths, only ten simulation runs with a fixed  $T_P$  are needed to identify the true worst-case code path, which takes a bit more than one minute. For a CP with a dozen of cores, this will take only dozens of minutes to pin down the worst-case code paths for all the cores.

Finally, for each core loaded with the worst-case code path, several simulation runs with different  $T_p$  values are performed to identify the maximum sustainable line rate for that core. This process is repeated for all the cores to identify the bottleneck pipeline stage for each core pipeline and finally the maximum sustainable line rate for the entire CP.

## 3.4 Simulation Testing

In this section, the accuracy of the proposed tool is tested against the CAS (Cycle-Accurate Simulators), i.e., IXP 1200/2400 SDK Developer workbenches [8] [9]. With a set of code samples available in both IXP1200/2400, the sustainable line rates obtained from our tool are compared with those from CAS. For all the code samples, there are only a few number of code paths for each core and we can afford to perform exhaustive search for the bottleneck core and the corresponding worst-case code path. For this reason, the simulation focuses on testing the accuracy of the simulation tool only, assuming the bottleneck core and the corresponding worst-case code path are known. The code samples and corresponding simulation setups are described in Section 3.4.1 and Section 3.4.2 presents the test results

## 3.4.1. Simulation Setup

Since all the cores in IXP1200/2400 run a coarse-grained thread scheduling discipline, our simulation tool is configured to run the coarse-grained thread scheduling algorithm as well.

The functions in the core topology for IXP1200 and IXP2400 sample applications are briefly described as follows.

IXP1200 code samples: Four different code samples, *Packet Count* [1], *Generic IPv4*Forwarding, Layer-2 Filtering, and ATM/Ethernet IP Forwarding, available in IXP1200 Developer workbench [8] are tested. The worst-case code paths at the bottleneck cores for these code samples are given in Appendix A. The complete implementation details can be found in the Intel IXP1200 building blocks application design guide with the Developer workbench. In the following description of code samples, we focus on the functions mapped to the bottleneck core.

Packet Count: this code sample counts the number of packets received. A receive thread checks for data on the MAC port, transfers packet from MAC port to receive buffers. After packet reception is complete, the thread moves the packet into SDRAM and reads the packet header into the core. A counter is maintained in SCRATCH and is incremented on receiving a packet.

Generic IPv4 Forwarding: after packet reception as in Packet Count, RFC1812 generic IPv4 forwarding is implemented in this code sample.

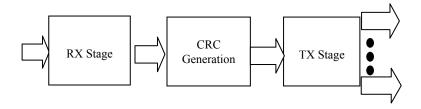

ATM/Ethernet IP Forwarding: This code sample is a mixed code implementation of ATM /Ethernet IP forwarding. Only Ethernet-to-ATM flow is considered in the test. The header checksum check, TTL update, and IP lookup are performed in the receive block after packet reception as in *Packet Count*. Then the LLC/SNAP and modified IP headers are written back into the SDRAM. When the frame fragment with EOP (End of Packet) information is received, AAL5 trailer information is written into the SDRAM buffer and the complete PDU is enqueued for CRC generation at the next pipeline stage.

Layer-2 filtering: This code example implements Ethernet protocol, MAC address filtering and layer 2 forwarding in the receive block after packets are received.

Packet Count, Generic IPv4 Forwarding, and Layer-2 Filtering code samples are mapped to two core pipelined stages as shown in Figure 3.6 and ATM/Ethernet Forwarding is

mapped to three core pipeline stages as shown in Figure 3.7. The original code samples are modified to allow only one core at the receive stage handling packets coming from a single port. As a result, the receive core becomes the bottleneck core to be tested. The code samples can also be changed to allow configuration of the number of threads from one to four.

Figure 3.6 Pipeline Configuration for Packet Count, Generic IP Forwarding and Layer-2 Filtering

Figure 3.7 Pipeline Configuration for ATM/Ethernet Forwarding

Packet Count, Generic IPv4 Forwarding, and Layer-2 Filtering code samples are mapped to two core pipelined stages as shown in Figure 3.6 and ATM/Ethernet Forwarding is mapped to three core pipeline stages as shown in Figure 3.7. The original code samples are modified to allow only one core at the receive stage handling packets coming from a single port. As a result, the receive core becomes the bottleneck core to be tested. The code samples can also be changed to allow configuration of the number of threads from one to four.

**IXP2400** code samples: *IPv4 Ethernet*, *DiffServ POS*, and *MPLS* in IXP2400 Developer workbench [9] are tested. Again, the associated code paths are given in Appendix A.

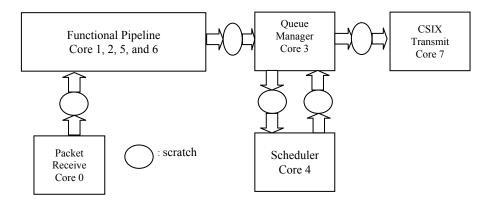

In what follows, the code samples are briefly explained. All of these applications have five blocks and the same pipeline configuration as shown in Figure 3.8. The complete implementation details can be found in the Intel IXP 2400 building blocks application design guide with the Developer workbench.

The first block is a packet receive block and uses a scratch ring to communicate with the next block. The second block is a functional block where application specific functional pipeline executes in parallel on four cores. The pipeline has five microblocks in DiffServ POS application: PPP decapsulation/classify microblock, 6-tuple classifier microblock, TCM meter microblock (ignored for our simulation setup: in case of no traffic profile in effect, packets may only pass through a classifier and a marker [RFC 2475]), DSCP Marker microblock and IPv4 forwarder microblock. In MPLS and IPv4 Ethernet applications, the pipeline consists of two microblocks: MPLS processing and IPv4 forwarder microblocks for MPLS and Ethernet decapsulation/classify/filter and IPv4 forwarder microblocks for IPv4 Ethernet. The third block is the queue manager which performs enqueue/dequeue operations on the hardware-assisted SRAM queues. The queue manager receives enqueue requests from the functional pipeline through a scratch ring. Another scratch ring is fed with dequeue requests from the CSIX scheduler. The fourth block is the CSIX scheduler which selects constant-length packet segments to be transmitted to the CSIX fabric. The final block is the CSIX transmit block which receives transmit messages from the queue manager and moves packet segments into a transmit buffer.

For all the IXP2400 code samples we tested, the number of threads in use is not configurable in the original code samples, which is fixed at eight. To test the functional block, three of the four cores are disabled and the remaining core creates a bottleneck at this block.

Figure 3.8 Ingress Blocks for IXP2400 Code Samples

Our simulation tool only needs to run a single core, corresponding to the bottleneck core for sample applications described above. The sustainable line rate for this bottleneck core is compared with that of CAS simulation involving the entire multi-stage pipeline. All the worst-case code paths for the corresponding bottleneck cores in table format are listed in Appendix A. The first column lists the task performed in each code path segment; the second column gives the segment length in terms of core clock cycles; the third column describes the type of resource accesses between segments; and the last column gives the unloaded resource access latency for each resource access. We assume that in the presence of resource access contentions, the resource access requests will be serviced based on a simple FIFO queuing mechanism. This means that unloaded resource access latencies and a set of simple resource access FIFO queues are the only IXP1200/2400 specific features or plug-ins used in our simulation tool. The rest are generic or common features pertaining to all the CP architectures. This indicates that our simulation tool is indeed generic and easily adaptable to a specific CP architecture. Clearly, the code paths as given in Appendix A can be easily derived from a piece of pseudo code provided by the user.

The parameter settings for the simulation are as follows:

IXP1200/2400: ME clock rate = 200/600 MHz, Packet size = 64/64 bytes,

SDRAM = 24/64MB, SRAM = 1/64 MB (for each channel of two).

#### 3.4.2. Test Results

In this Section, we compare sustainable line rates obtained from our tool with those obtained from IXP1200/2400 CAS for the code samples described in Section 3.4.1. Tables 3.1 through 3.4 give the results for different cases in similar formats. For IXP 1200 case studies in Tables 3.1 through 3.4, the first column gives the number of threads configured; the second and the third columns list the core latencies and the sustainable line rates obtained from our tool and CAS, respectively. The last column lists the percentage difference between the two sets of results. The table format for IXP2400 case studies in Table 3.5 is similar to the ones for IXP 1200 case studies, except the first column, where now the applications are listed, rather than the number of threads, which for IXP2400 is fixed at eight. As one can see, for all the cases studied, the results obtained from our tool are within 6% of the CAS results. Moreover, each simulation run finishes in a few seconds on a Pentium 4 Computer. Since there are significant differences between IXP1200 and IXP2400 architectures, such consistent agreement of the two provides strong evidence, indicating that our tool can serve as an effective tool to aid the initial programming of a CP as well as new CP architecture design.

Finally, we note that in all the code samples, there is a critical section in the receive stage. In particular, the critical section dominates the code path of the *Packet Count* sample, constituting about 67% of the total code path, from the first task to the 6<sup>th</sup> task in the code path for Packet Count Sample given in Appendix A. This dominant serialization effect causes the line rate to decrease when more than two threads are configured as shown in Table 3.1. This effect is successfully captured by our tool, which accounts for the impact of the critical section by recognizing the start and end of critical section events in the code path. Interested readers may

refer to [10] for detailed explanation on why this critical section causes the decrease of line rate when adding more than two threads.

Table 3.1 Tool versus CAS (IXP1200) for *Packet Counting*

|         | Too                           |                           | (   | CAS | % Error rate  |  |

|---------|-------------------------------|---------------------------|-----|-----|---------------|--|

| Threads | Total Latency(TL)<br>(cycles) | Receive rate R1<br>(Mbps) | TL  | R2  | R1-R2 *100/R2 |  |

| 1       | 296                           | 334                       | 293 | 337 | 0.89          |  |

| 2       | 375                           | 525                       | 380 | 518 | 1.40          |  |

| 3       | 645                           | 460                       | 627 | 473 | 2.74          |  |

| 4       | 875                           | 450                       | 856 | 460 | 2.17          |  |

Table 3.2 Tool versus CAS (IXP1200) for Generic IPv4 Forwarding

| <b>-</b> | To  | ool | CA  | AS  | 0.7          |

|----------|-----|-----|-----|-----|--------------|

| Threads  | TL  | R1  | TL  | R2  | % Error rate |

| 1        | 560 | 183 | 537 | 183 | 0.00         |

| 2        | 590 | 347 | 600 | 328 | 5.79         |

| 3        | 687 | 447 | 687 | 431 | 3.71         |

| 4        | 936 | 438 | 876 | 449 | 2.45         |

Table 3.3 Tool versus CAS (IXP1200) for ATM/Ethernet IP Forwarding

| Threads  | To   | ool | CAS  | 3   | % Error rate |  |

|----------|------|-----|------|-----|--------------|--|

| Tilleaus | TL   | R1  | TL   | R2  | % EITOI Tale |  |

| 1        | 732  | 140 | 724  | 140 | 0.00         |  |

| 2        | 830  | 247 | 812  | 250 | 1.20         |  |

| 3        | 985  | 312 | 981  | 311 | 0.32         |  |

| 4        | 1260 | 326 | 1184 | 343 | 4.96         |  |

Table 3.4 Tool versus CAS (IXP1200) for *Layer-2 Filtering*

| Threads  | To   | ool | CAS  | 3   | % Error rate |

|----------|------|-----|------|-----|--------------|

| Tilleaus | TL   | R1  | TL   | R2  | % Enormate   |

| 1        | 735  | 140 | 730  | 140 | 0.00         |

| 2        | 816  | 251 | 798  | 257 | 2.33         |

| 3        | 960  | 320 | 978  | 314 | 1.91         |

| 4        | 1168 | 351 | 1304 | 354 | 0.85         |

Table 3.5 Tool versus CAS (IXP2400) with 8 Threads

| Applications  | Too  | ol  | C    | AS  | % Error rate |  |

|---------------|------|-----|------|-----|--------------|--|

| Applications  | TL   | R1  | TL   | R2  | % ⊑HOLTALE   |  |

| Diffserv Pos  | 2960 | 830 | 2950 | 832 | 0.24         |  |

| MPLS          | 2824 | 870 | 2750 | 890 | 2.25         |  |

| IPv4 Ethernet | 2898 | 849 | 2935 | 839 | 1.19         |  |

#### 3.5 Related Work

There are a vast number of processor simulation tools available [1] [12-26] (e.g. cycle-accurate, allowing detailed timing analysis, and providing primitives for flexible component modeling). Particularly relevant to our work are the Network Processor analysis tools (e.g., [1] [16-24]).

Most CP simulation software (e.g., [16-19]) aims at providing rich features to allow detailed statistical or per-packet analysis, which is useful for program fine tuning, rather than fast CP performance testing. Even for the most lightweight CP simulator described in [16], it is reported that to simulate one second of hardware execution, it takes 1 hour on a Pentium III 733 PC. Moreover, it assumes the availability of the executable program or microcode as input for the simulation. On the other hand, the algorithms for data path functions to CP core topology mapping (e.g., [21] [23] [24]) are generally fast, but at the expense of having to overlook many essential processing details that may have an impact on the overall system performance. To make the problem tractable, a common technique used in these approaches is to partition the

data path functions into tasks and each task is then associated with one or multiple known resource demand metrics, e.g., the core latency and program size. Then an optimization problem under the demand constraints is formulated and solved to find a feasible/optimal mapping of those tasks to a pipelined/parallel core topology. Since the actual resource demand metrics for each task are, in general, complex functions of mapping itself, and are a strong function of the number of threads and thread scheduling discipline in use at each core, these approaches cannot provide mappings with high accuracy. Although the approach in [23] accounts for certain multithreading effect, it only works for a single memory access and under a coarse-grained scheduling discipline.

From previous work, all the above existing tools lack of the following feature needed to address the problem at hand. Namely, they are not concerned with how the packet input process should be generated, which is assumed to be provided by the user, rather than part of the tool design. Given that there are virtually unlimited numbers of possible packet arrival processes and mixtures of packets carrying various code paths, it is a daunting task for a user of an existing tool to decide what input processes should be tested, or what statistics should be collected. Note that no matter how fast a simulation tool may be, the simulation time is guaranteed to be prohibitively long if the goal is to perform exhaustive statistical analysis, based on the simulation data collected from a large number of packet arrival processes and mixtures of code paths

#### **CHAPTER 4**

#### A THEORETICAL FAMEWORK FOR DESIGN SPACE EXPLORATION

In this chapter, we develop a theoretical framework for a large design space based on the methodology introduced in Chapter 2. Section 4.1 introduces the queuing network model that covers the entire design space in Figure 2.4. Section 4.2 proposes an iteration algorithm that addresses the scalability issue concerning the queuing network modeling technique, as explained in Section 2.2. Section 4.3 provides the testing results in a large design space for the proposed analytic model versus simulation results using the simulation tool developed in Chapter 3. Finally, Section 4.4 discusses the related work.

## 4.1 Queuing Network Model

For MPs in the design space covered by the queuing network models in chapter 2, all the performance measures can be derived from a generation function, which is described mathematically as follows.

First, we define N as the total number of jobs (or threads) for the entire system and it follows that,

$$N = \sum_{i=1}^{M} k_i, \qquad k_i = \sum_{r=1}^{R} k_{ir}, \qquad (4.1)$$

where  $k_{ir}$  is the number of jobs in the rth job class at the node i and M is the total number of queuing servers and R is the number of job classes in the system.

According to the BCMP theorem [27], the state probabilities of the system can be written as:

$$\pi(\mathbf{S}_1, \dots, \mathbf{S}_M) = \frac{1}{G(\mathbf{N})} \prod_{i=1}^M f_i(\mathbf{S}_i), \tag{4.2}$$

where the state of the *i*th node is  $\mathbf{S}_i = (k_{i1}, ..., k_{iR})$  and the population vector containing the total number of jobs is  $\mathbf{N} = \sum_{i=1}^{M} \mathbf{S}_i$  and  $\mathbf{G}(\mathbf{N})$  is the so-called normalization constant or generation function of the system and it is given by:

$$G(\mathbf{N}) = \sum_{\sum_{i=1}^{M} \mathbf{S}_i = \mathbf{N}} \prod_{i=1}^{M} f_i(\mathbf{S}_i), \tag{4.3}$$

The  $f_i(\mathbf{S}_i)$ 's are the relative state probabilities of the state  $\mathbf{S}_i$  at the node i, which are defined as follows:

$$f_{i}(\mathbf{S}_{i}) = \begin{cases} k_{i}! \frac{1}{\beta_{i}(k_{i})} \cdot \left(\frac{1}{\mu_{i}}\right)^{k_{i}} \cdot \prod_{r=1}^{R} \frac{1}{k_{ir}!} e_{ir}^{k_{ir}}, & \text{for } -/\text{ M/m} - \text{FCFS,} \end{cases}$$

$$k_{i}! \prod_{r=1}^{R} \frac{1}{k_{ir}!} \cdot \left(\frac{e_{ir}}{\mu_{ir}}\right)^{k_{ir}}, & \text{for } -/\text{G/1} - \text{PS \& LCFS PR,}$$